gujjubhai123

Newbie level 4

hello,

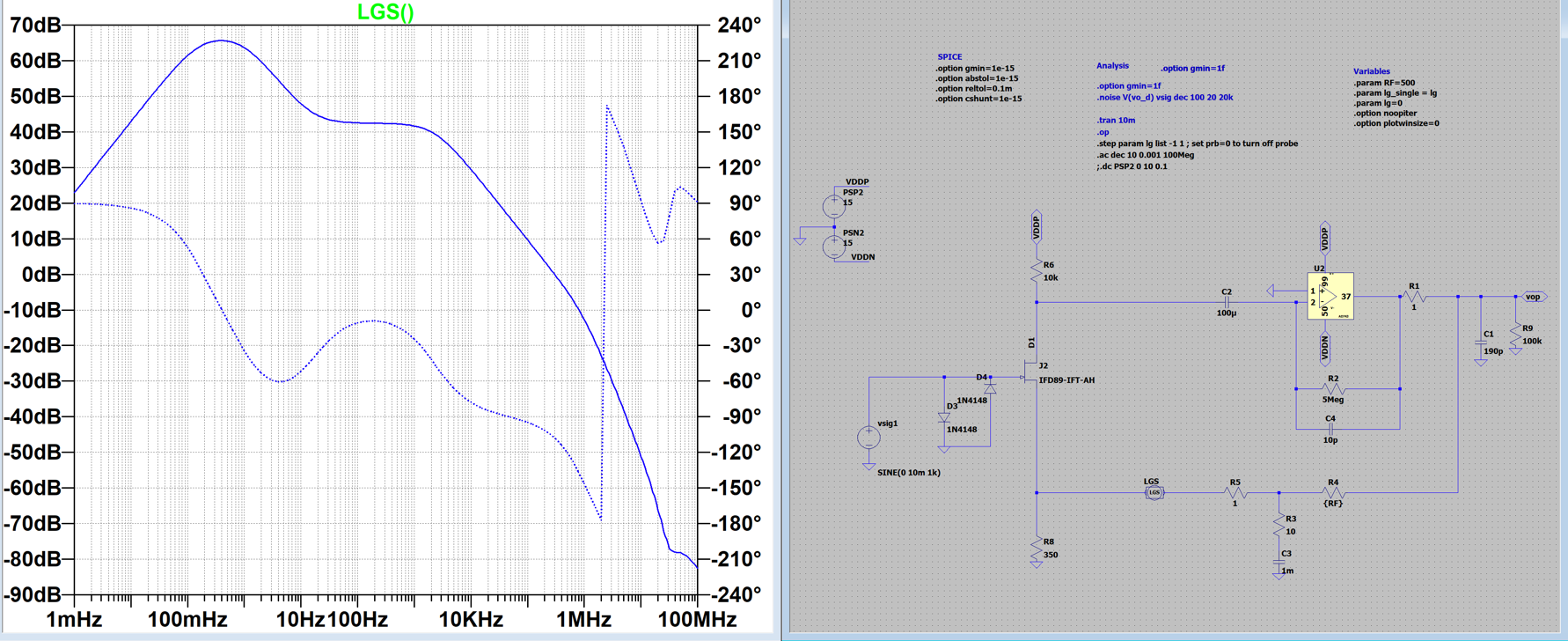

I have build this amplifier. In lab, I am applying 10mV rms at the input. At output I see 400mV-rms at time=0s. And over 3.5minutes, the output rises from 400mV-rms to 500mV-rms. The expected output is 500mV-rms. After the output crosses say 504mV, the amplifier becomes UNSTABLE.

I plotted loopgain vs frequency. When dB(LG) crosses 0dB, the phase(LG) has passed by 180deg w.r.t. the starting phase of 90deg at 1mHz. Do you agree with that assessment that this amplifier with such a LG is unstable? "LG" is the probe inserted in the outer loop.

What's causing the 3.5minute transient?

Your input is greatly appreciated!

Loopgain method: "LG" developed by (c) Sandro Herrera, SW Audio.

[1] Michael Tian, V. Visvanathan, Jeffrey Hantgan, and Kenneth Kundert,

"Striving for Small-Signal Stability", IEEE Circuits and Devices Magazine,

vol. 17, no. 1, pp. 31-41, January 2001.

I have build this amplifier. In lab, I am applying 10mV rms at the input. At output I see 400mV-rms at time=0s. And over 3.5minutes, the output rises from 400mV-rms to 500mV-rms. The expected output is 500mV-rms. After the output crosses say 504mV, the amplifier becomes UNSTABLE.

I plotted loopgain vs frequency. When dB(LG) crosses 0dB, the phase(LG) has passed by 180deg w.r.t. the starting phase of 90deg at 1mHz. Do you agree with that assessment that this amplifier with such a LG is unstable? "LG" is the probe inserted in the outer loop.

What's causing the 3.5minute transient?

Your input is greatly appreciated!

Loopgain method: "LG" developed by (c) Sandro Herrera, SW Audio.

[1] Michael Tian, V. Visvanathan, Jeffrey Hantgan, and Kenneth Kundert,

"Striving for Small-Signal Stability", IEEE Circuits and Devices Magazine,

vol. 17, no. 1, pp. 31-41, January 2001.