darthachill

Newbie level 3

Hi everybody,

today I have a problem conected with design asynchronous Counter mod 12 D.

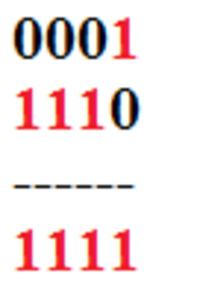

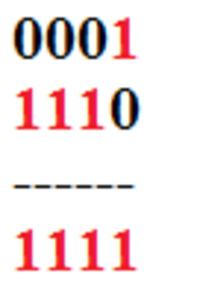

I use OR4 to detect for a while state "1111", because I want to reset counter to state "1101", but it's not working...

On symulation we can see that Counter reset his state after detected state "0111", before was state"1000", so counter detected it as state "1111" because it's asynchronous.

How can I solve this problem?

I should like to express my thanks for your support.

today I have a problem conected with design asynchronous Counter mod 12 D.

I use OR4 to detect for a while state "1111", because I want to reset counter to state "1101", but it's not working...

On symulation we can see that Counter reset his state after detected state "0111", before was state"1000", so counter detected it as state "1111" because it's asynchronous.

How can I solve this problem?

I should like to express my thanks for your support.