jonnybgood

Full Member level 4

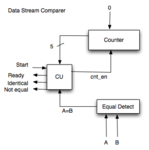

I designed a hardware block diagram for a system that checks if two data streams (each 32-bits long) are identical.

As a black box, the system has Data A, data B, Start, Clk, reset, Ready (for when all 32-bits are checked), Identical (after 32-bits checked and all the same), Not_equal (when the two stream are not identical). Each output signal must be only after all the 32-bits are checked.

Attached is my attempt for the hardware block diagram, and ASM. Are there an flaws in my design so far? After I need to convert the ASM to an FSM but I am not sure I have to consider all the states since the FSM would need 64 states due to the 32-bit long stream (log_2_32 = 5) and the A==B bit (to remember). thanks

As a black box, the system has Data A, data B, Start, Clk, reset, Ready (for when all 32-bits are checked), Identical (after 32-bits checked and all the same), Not_equal (when the two stream are not identical). Each output signal must be only after all the 32-bits are checked.

Attached is my attempt for the hardware block diagram, and ASM. Are there an flaws in my design so far? After I need to convert the ASM to an FSM but I am not sure I have to consider all the states since the FSM would need 64 states due to the 32-bit long stream (log_2_32 = 5) and the A==B bit (to remember). thanks