circuitking

Full Member level 5

Hi all,

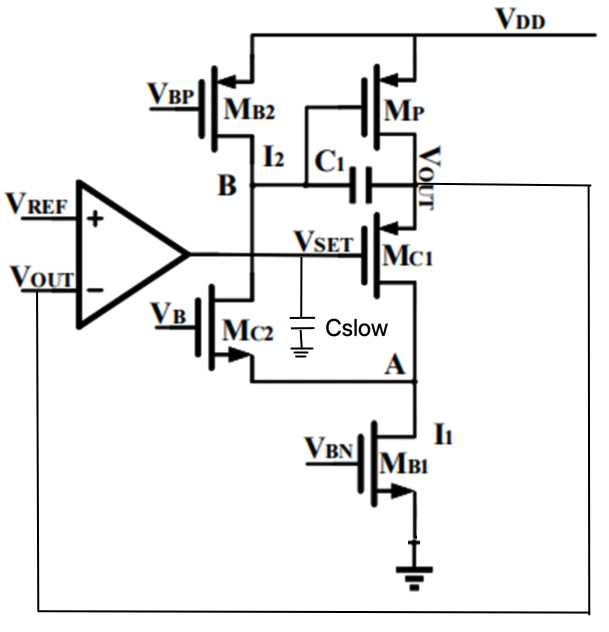

I would like to analyse the circuit.

how to draw the small signal model for the two loop circuit below.

How to calculate the pole frequencies from each loop

How to calculate the PSRR of the circuit

How do I determine the value of the C1 and Cslow so that the circuit is stable?

What should be the specifications of the opamp such as, gbw, gain.. etc

How to do the first cut design for the circuit.

Any help is appreciated thanks

I would like to analyse the circuit.

how to draw the small signal model for the two loop circuit below.

How to calculate the pole frequencies from each loop

How to calculate the PSRR of the circuit

How do I determine the value of the C1 and Cslow so that the circuit is stable?

What should be the specifications of the opamp such as, gbw, gain.. etc

How to do the first cut design for the circuit.

Any help is appreciated thanks