0987654321

Newbie level 3

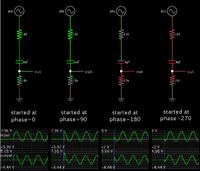

can somebody tell me that how to by pass the A.C signal from a A.C +D.C signal

such that there should not be any time lag between input signal and the output signal,

which means its not supposed to use capacitor.

A.C signal frequency is of range 8-80 hz.

Is there any method to take only the a.c signal retaining the d.c behind with time lag.

plz help me..

here is the link of figure.

https://obrazki.elektroda.pl/2897723500_1369826637.jpg[/U]

such that there should not be any time lag between input signal and the output signal,

which means its not supposed to use capacitor.

A.C signal frequency is of range 8-80 hz.

Is there any method to take only the a.c signal retaining the d.c behind with time lag.

plz help me..

here is the link of figure.

https://obrazki.elektroda.pl/2897723500_1369826637.jpg[/U]