michaelScott

Junior Member level 2

Hello people,

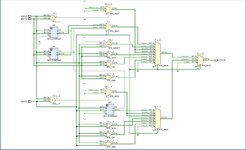

I am designing a RISCV ALU on VIVADO and i want all the instructions as sub-blocks as seen the code below(carry-lookahead adder/subtractor). I want only one carry-lookahead adder/subtractor in the ALU for the different instructions like add and subtract. Can you help me about that. In the output i see only high impedance.

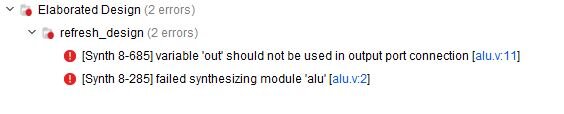

I improved the design as seen below but i get error about the out signal.

What do i do wrong.

thanks in advance

I am designing a RISCV ALU on VIVADO and i want all the instructions as sub-blocks as seen the code below(carry-lookahead adder/subtractor). I want only one carry-lookahead adder/subtractor in the ALU for the different instructions like add and subtract. Can you help me about that. In the output i see only high impedance.

Code:

`timescale 1ns / 1ps

module alu(

input [31:0] X, //instruction input

input [31:0] A, //data input

input [31:0] B, //data input

output reg [31:0] C

);

wire [31:0] add, sum;

wire C5;

carry_lookahead M0(A, B, 0, add, C5);

carry_lookahead M1(A, B, 1, sum, C5);

///////////////////////// R TYPE /////////////////////////

wire [6:0] funct7;

//reg [4:0] rs2; //address

//reg [4:0] rs1; //address

wire [2:0] funct3;

//reg [4:0] rd; //address

wire [6:0] opcode;

///////////////////////// I TYPE /////////////////////////

wire [11:0] imm;

//reg [4:0] rs1; //register adress

//wire [2:0] funct3;

//reg [4:0] rd; //register adress

//wire [6:0] opcode;

///////////////////////////////////////////////////////////

wire [31:0] imm_i;

assign imm_i = {{20{imm[11]}}, imm[11:0]};

wire [31:0] sum_imm;

carry_lookahead M2(A, imm_i, 0, sum_imm, C5);

assign funct7 = X[31:25];

//assign rs2 = X[24:20];

//assign rs1 = X[19:15];

assign funct3 = X[14:12];

//assign rd = X[11:7];

assign opcode = X[6:0];

assign imm = X[31:20];

always @(funct7[5], funct3, opcode, A, B)

begin

C = 0;

case (opcode)

7'b0110011: case(funct3)

3'b000: case(funct7[5])

1'b0: C = add; //add

1'b1: C = sum; //sum

endcase

3'b001: C = A << B; //sll

3'b010: C = (A < B) ? 1'b1 : 1'b0; //slt(signed)

3'b011: C = (A < B) ? 1'b1 : 1'b0; //sltu(unsigned)

3'b100: C = A ^ B; //xor

3'b110: C = A | B; //or

3'b111: C = A & B; //and

endcase

7'b0010011: case(funct3)

3'b000: C = sum_imm; //addi

3'b010: C = (A < imm_i) ? 1'b1 : 1'b0; //slti(signed)

3'b011: C = (A < imm_i) ? 1'b1 : 1'b0; //sltiu(signed)

3'b100: C = A ^ imm_i;//xori

3'b110: C = A | imm_i;//ori

3'b111: C = A & imm_i;//andi

endcase

endcase

end

endmodule

--- Updated ---

I improved the design as seen below but i get error about the out signal.

What do i do wrong.

thanks in advance

Code:

`timescale 1ns / 1ps

module alu(

input [31:0] X, //instruction input

input [31:0] A, //data input

input [31:0] B, //data input

output reg [31:0] C

);

reg [31:0] in1, in2, out;

reg M, C5;

carry_lookahead M0(in1, in2, M, out, C5);

///////////////////////// R TYPE /////////////////////////

wire [6:0] funct7;

//reg [4:0] rs2; //address

//reg [4:0] rs1; //address

wire [2:0] funct3;

//reg [4:0] rd; //address

wire [6:0] opcode;

///////////////////////// I TYPE /////////////////////////

wire [11:0] imm;

//reg [4:0] rs1; //register adress

//wire [2:0] funct3;

//reg [4:0] rd; //register adress

//wire [6:0] opcode;

///////////////////////////////////////////////////////////

wire [31:0] imm_i;

assign imm_i = {{20{imm[11]}}, imm[11:0]};

assign funct7 = X[31:25];

//assign rs2 = X[24:20];

//assign rs1 = X[19:15];

assign funct3 = X[14:12];

//assign rd = X[11:7];

assign opcode = X[6:0];

assign imm = X[31:20];

always @(funct7[5], funct3, opcode)

begin

C = 0;

case (opcode)

7'b0110011: case(funct3)

3'b000: case(funct7[5])

1'b0: begin

in1 = A;

in2 = B;

M = 0;

out = C; //add

end

1'b1: begin

in1 = A;

in2 = B;

M = 1;

out = C; //sum

end

endcase

3'b001: C = A << B; //sll

3'b010: C = (A < B) ? 1'b1 : 1'b0; //slt(signed)

3'b011: C = (A < B) ? 1'b1 : 1'b0; //sltu(unsigned)

3'b100: C = A ^ B; //xor

3'b110: C = A | B; //or

3'b111: C = A & B; //and

endcase

7'b0010011: case(funct3)

3'b000: begin

in1 = A;

in2 = imm_i;

M = 0;

out = C; //addi

end

3'b010: C = (A < imm_i) ? 1'b1 : 1'b0; //slti(signed)

3'b011: C = (A < imm_i) ? 1'b1 : 1'b0; //sltiu(signed)

3'b100: C = A ^ imm_i;//xori

3'b110: C = A | imm_i;//ori

3'b111: C = A & imm_i;//andi

endcase

endcase

end

endmoduleAttachments

Last edited: