szabo.tivadar

Newbie level 2

Hi

I'm facing a weird problem and I don't really understand the error I get. Please help me if you're smarter than me 8)

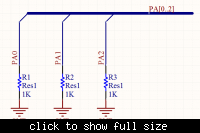

I create a blank new project, set the net ID scope to hierarchical. This way every net label should be a local one (except power ones). I create 2 subsheets and put a few wires with net labels in them. PA0, PA1, PA2 in the 1st sheet and the same in the second one. No ports, just the main sheet and 2 subsheets, this way there's no connection between the 2 subsheet, compiles w/o errors, so far so good.

I want to put those PAs into a bus: PA[0..2] in both subsheets, however if I connect those wires to a bus and name both buses PA[0..2], the compiler gives me a "duplicate net names bus slice" error. Why? Isn't the bus supposed to be local?

I attach a picture of a subsheet, the other one is the same.

Thank you for your time.

I'm facing a weird problem and I don't really understand the error I get. Please help me if you're smarter than me 8)

I create a blank new project, set the net ID scope to hierarchical. This way every net label should be a local one (except power ones). I create 2 subsheets and put a few wires with net labels in them. PA0, PA1, PA2 in the 1st sheet and the same in the second one. No ports, just the main sheet and 2 subsheets, this way there's no connection between the 2 subsheet, compiles w/o errors, so far so good.

I want to put those PAs into a bus: PA[0..2] in both subsheets, however if I connect those wires to a bus and name both buses PA[0..2], the compiler gives me a "duplicate net names bus slice" error. Why? Isn't the bus supposed to be local?

I attach a picture of a subsheet, the other one is the same.

Thank you for your time.