I_THINK_ITS_SHORTED

Newbie level 4

I'm having some trouble getting serial SRAM to work using the Altera DE2-115. I tried using the "SPI (3 Wire Serial)" IP core, but after mapping the exported signals to the GPIO pins I can't seem to properly control the memory. I'm also not sure if its a problem that the SRAM is 4 wire SPI, since all 4 necessary signals are present in the "3 wire" serial IP core.

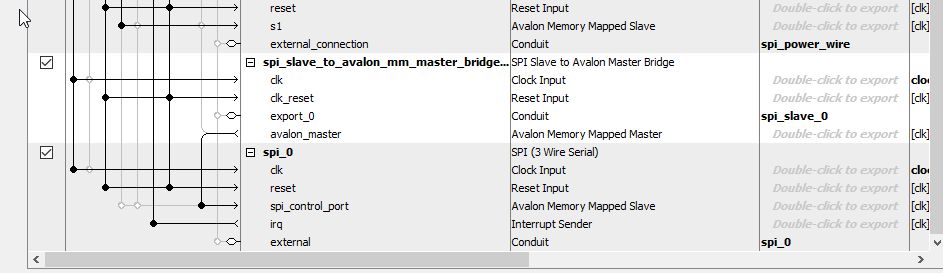

I suspect my problem has to do with my Qsys setup, specifically the connections between the SPI components, as shown below.

Not sure how I should be configuring the connections for a simple 4 wire SPI. I tried just the 3 wire component on its own but that didn't seem to work, however that may have been the fault of my code. The documentation has me thinking that the bridge might be required for memory mapped access to the SPI, but I'm not sure of that either. Thanks in advance for any help offered.

I suspect my problem has to do with my Qsys setup, specifically the connections between the SPI components, as shown below.

Not sure how I should be configuring the connections for a simple 4 wire SPI. I tried just the 3 wire component on its own but that didn't seem to work, however that may have been the fault of my code. The documentation has me thinking that the bridge might be required for memory mapped access to the SPI, but I'm not sure of that either. Thanks in advance for any help offered.