promach

Advanced Member level 4

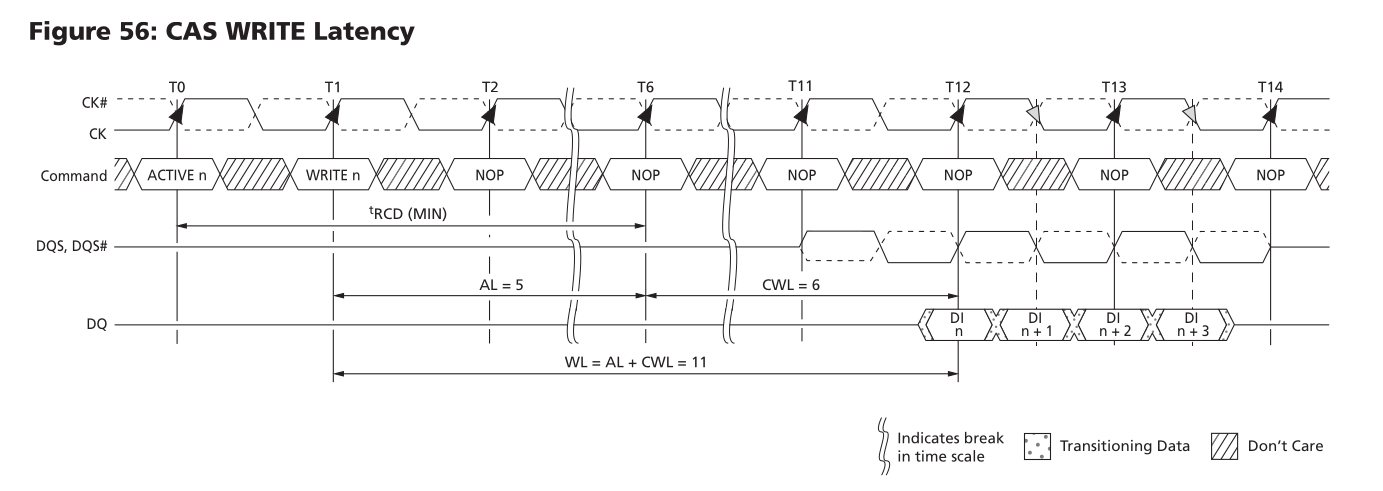

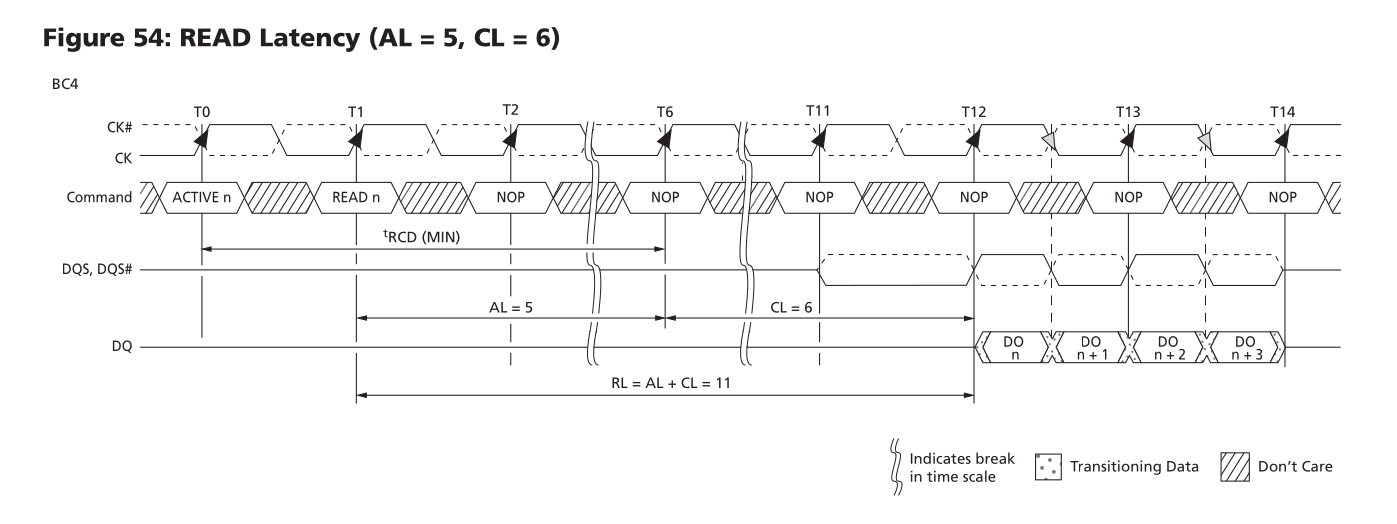

In TN-47-10 – DDR2 Posted CAS# Additive Latency Technical Note , what does it exactly mean by Additive latency (AL = 1) is only used for READ commands and will not affect WRITE command timing ?