Junus2012

Advanced Member level 5

- Joined

- Jan 9, 2012

- Messages

- 1,552

- Helped

- 47

- Reputation

- 98

- Reaction score

- 53

- Trophy points

- 1,328

- Location

- Italy

- Activity points

- 15,235

Dear friends,

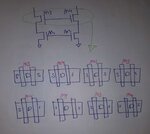

below are the suggeted three connection of dummy transistors to the cascoded circuit.

In the first two schemes the dummy transistors are off as thier VGS tied to zero. However,

in scheme 1, the drain of the dummy transistors are connected to the drain of the matched transistors. Thus it adds parasatic capacitance. This procedure I followed here in this formum as was suggested that dummy transistors better to share net with the matched array. I dont understand why shoud be ?

Therefore, I tried to plot scheme 2 where dummy transistors share nothing with the matched array, all the terminals are tied to ground , NMOS is off and no issue should be. Here must be no load effect on the matched array, and in my opinion it should be better, but I need your point of view please.

in the last scheme 3, that is from Allen Holberg, he shared the gate between dummy and the matched array, in my opinion it will be rise the Cox so it increase the parasatic capacitnace more than scheme 1.

Finally, Cadence bring my attension when I am learning to put dummy from MODGEN. he was giving two options, active dummy which is connected to a net or inactive, and I think I provided both in the presented schemes.

Looking forward to your discussion

Best Regards

below are the suggeted three connection of dummy transistors to the cascoded circuit.

In the first two schemes the dummy transistors are off as thier VGS tied to zero. However,

in scheme 1, the drain of the dummy transistors are connected to the drain of the matched transistors. Thus it adds parasatic capacitance. This procedure I followed here in this formum as was suggested that dummy transistors better to share net with the matched array. I dont understand why shoud be ?

Therefore, I tried to plot scheme 2 where dummy transistors share nothing with the matched array, all the terminals are tied to ground , NMOS is off and no issue should be. Here must be no load effect on the matched array, and in my opinion it should be better, but I need your point of view please.

in the last scheme 3, that is from Allen Holberg, he shared the gate between dummy and the matched array, in my opinion it will be rise the Cox so it increase the parasatic capacitnace more than scheme 1.

Finally, Cadence bring my attension when I am learning to put dummy from MODGEN. he was giving two options, active dummy which is connected to a net or inactive, and I think I provided both in the presented schemes.

Looking forward to your discussion

Best Regards