aminpix

Full Member level 2

I have a zynq FPGA and I am trying to read a file from MicroSD, then write the file into the BRAM of the FPGA and do some process on them in PL side of the Zynq.

I can read and write to the BRAM from PL side.

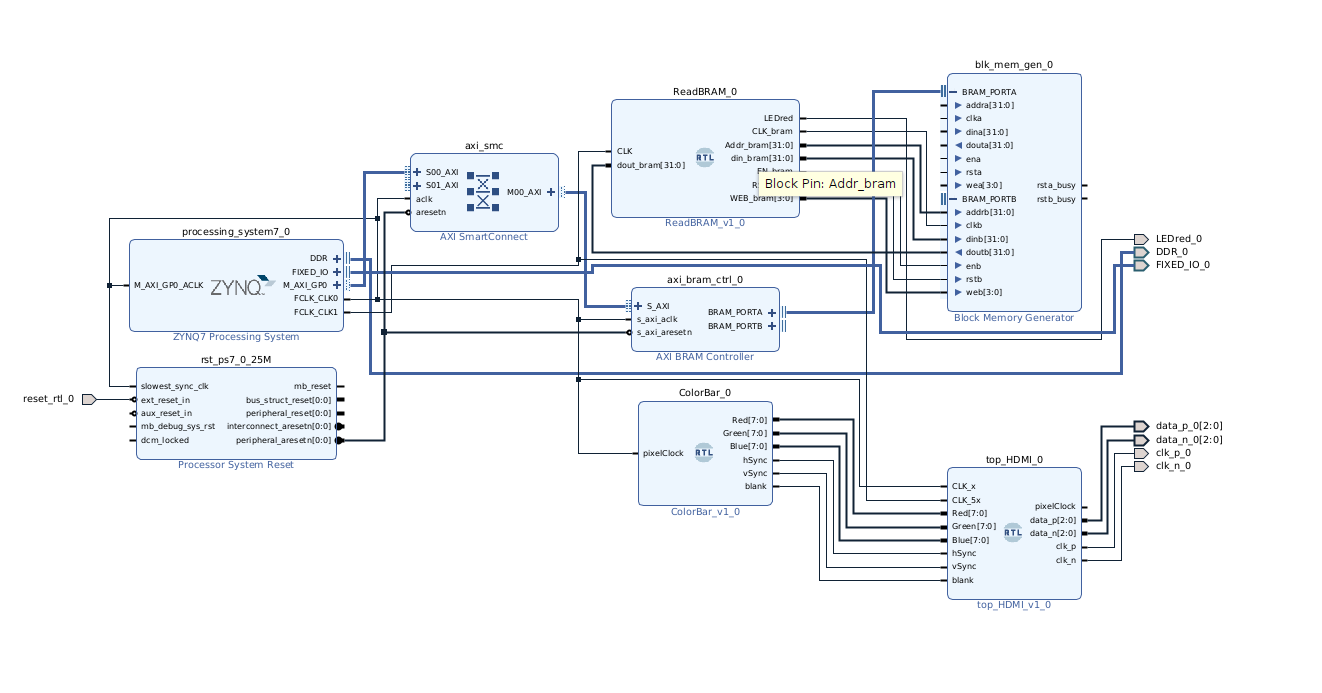

The block diagram is like this:

and my PS code is this:

Now, I just want to read BRAM from PS (and next step will be write into the BRAM).

What is wrong with my code?

I can read and write to the BRAM from PL side.

The block diagram is like this:

and my PS code is this:

Code:

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xparameters.h"

int main()

{

init_platform();

UINTPTR ADRS1 ;

u32 din ;

int i ;

ADRS1 = XPAR_BRAM_0_BASEADDR ;

while (1)

{

usleep(1000000);

for (i=0;i<50;i++)

{

din = *((uint32_t *)(ADRS1 + i)); //(uint32_t)*(ADRS1+i);

printf("val %i: %lu \n\r",i, din);

}

}Now, I just want to read BRAM from PS (and next step will be write into the BRAM).

What is wrong with my code?