ljp2706

Full Member level 2

Hello,

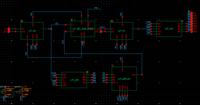

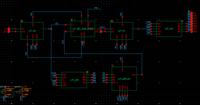

Currently, I am trying to design an 8-Bit Pipelined ADC. What I have completed so far is:

4 Bit FLASH ADC

4 Bit Resistor String DAC

Sample and Hold Circuit

Summation and Gain stage

My reference voltage is 0V, VDD=1V, VSS=-1V.

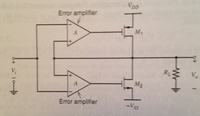

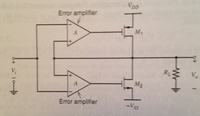

For the sample and hold circuit, I have a near minimum sized Transmission gate switch connected to a capacitor, the output is buffered using the embedded source unity gain buffer in the image below.

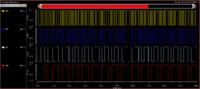

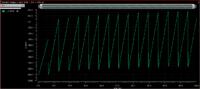

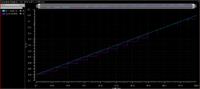

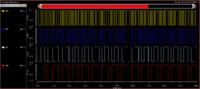

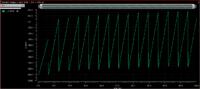

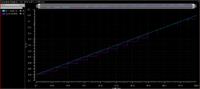

For some reason, my residue waveform seems to be shifted up which results in missing bits for the second stage conversion(I've attached a simulation of this). The first 4 Bits in the first stage are working as expected.

While I do think that the gain stage is responsible for the fact that the residue plot is not across the full scale voltage range, I do not think it is responsible for the vertical shift in the plot. I used an ideal source(voltage controlled voltage source) and this still occurs. What is causing this issue? I have been unable to isolate it.

Thank you!

Currently, I am trying to design an 8-Bit Pipelined ADC. What I have completed so far is:

4 Bit FLASH ADC

4 Bit Resistor String DAC

Sample and Hold Circuit

Summation and Gain stage

My reference voltage is 0V, VDD=1V, VSS=-1V.

For the sample and hold circuit, I have a near minimum sized Transmission gate switch connected to a capacitor, the output is buffered using the embedded source unity gain buffer in the image below.

For some reason, my residue waveform seems to be shifted up which results in missing bits for the second stage conversion(I've attached a simulation of this). The first 4 Bits in the first stage are working as expected.

While I do think that the gain stage is responsible for the fact that the residue plot is not across the full scale voltage range, I do not think it is responsible for the vertical shift in the plot. I used an ideal source(voltage controlled voltage source) and this still occurs. What is causing this issue? I have been unable to isolate it.

Thank you!