lei6042

Newbie level 5

hi,all

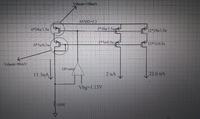

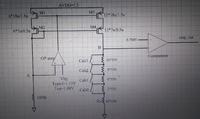

I deigned a group of current mirrors with current ratio of 6:1:12.

That is achieved by pmos ratio of 6*18u/1.5u : 1*18u/1.5u : 12*18u/1.5u.

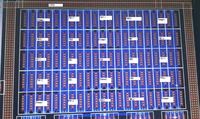

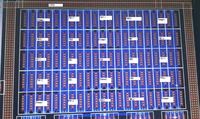

For better matching, I use centroid layout:

Pick the 1*18u/1.5u PMOS (PM1)as "cell" and put it in the center, outside which is the 6 cells (PM6).

Then the 12 cells (PM12) is around PM1 and PM6. Just as the attached pic shows!

Surperisingly, test results shows a 60% mismatch of current. I fail to find the cause of this huge error.

BTW, vdast of the PMOS's is about 100mV. For current matching,that is not a ideal value.

But how can it be so far away from the original desin?

Anyone here has idea about that? Thanks a lot ahead of time!

I deigned a group of current mirrors with current ratio of 6:1:12.

That is achieved by pmos ratio of 6*18u/1.5u : 1*18u/1.5u : 12*18u/1.5u.

For better matching, I use centroid layout:

Pick the 1*18u/1.5u PMOS (PM1)as "cell" and put it in the center, outside which is the 6 cells (PM6).

Then the 12 cells (PM12) is around PM1 and PM6. Just as the attached pic shows!

Surperisingly, test results shows a 60% mismatch of current. I fail to find the cause of this huge error.

BTW, vdast of the PMOS's is about 100mV. For current matching,that is not a ideal value.

But how can it be so far away from the original desin?

Anyone here has idea about that? Thanks a lot ahead of time!