Easy peasy

Advanced Member level 6

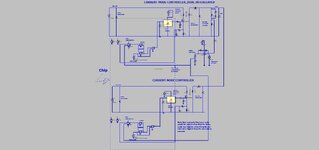

Is there a really basic 2 phase ( or 3 phase ) boost control IC out there with low side gate drive ? 0 - ~90% duty cycle on each output ( overlapping as it is boost 2 phase ) - ideally curr mode - but not fussy - any solution that only goes to 49% D on each o/p is no good.