sujan2

Newbie level 6

Hello Everyone,

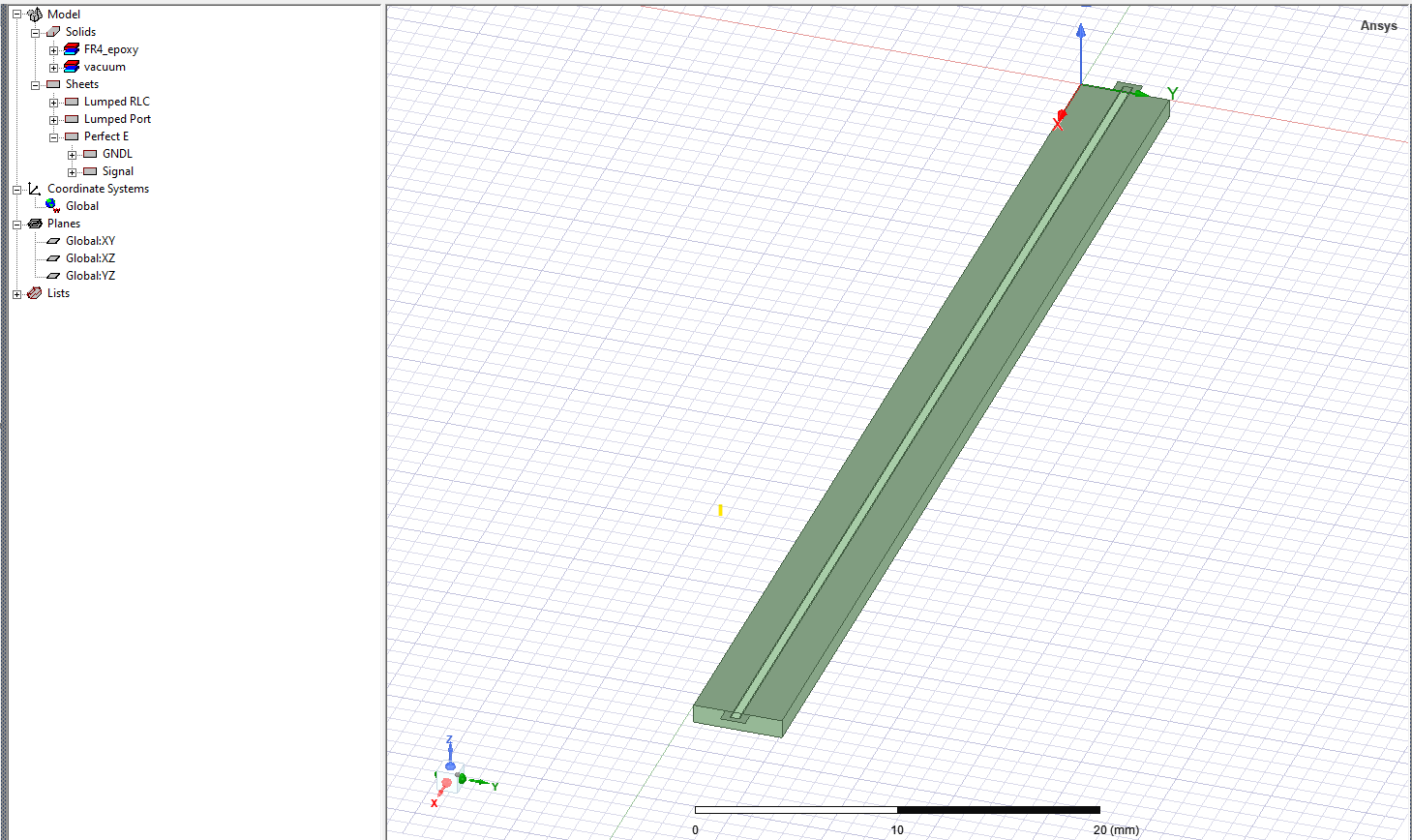

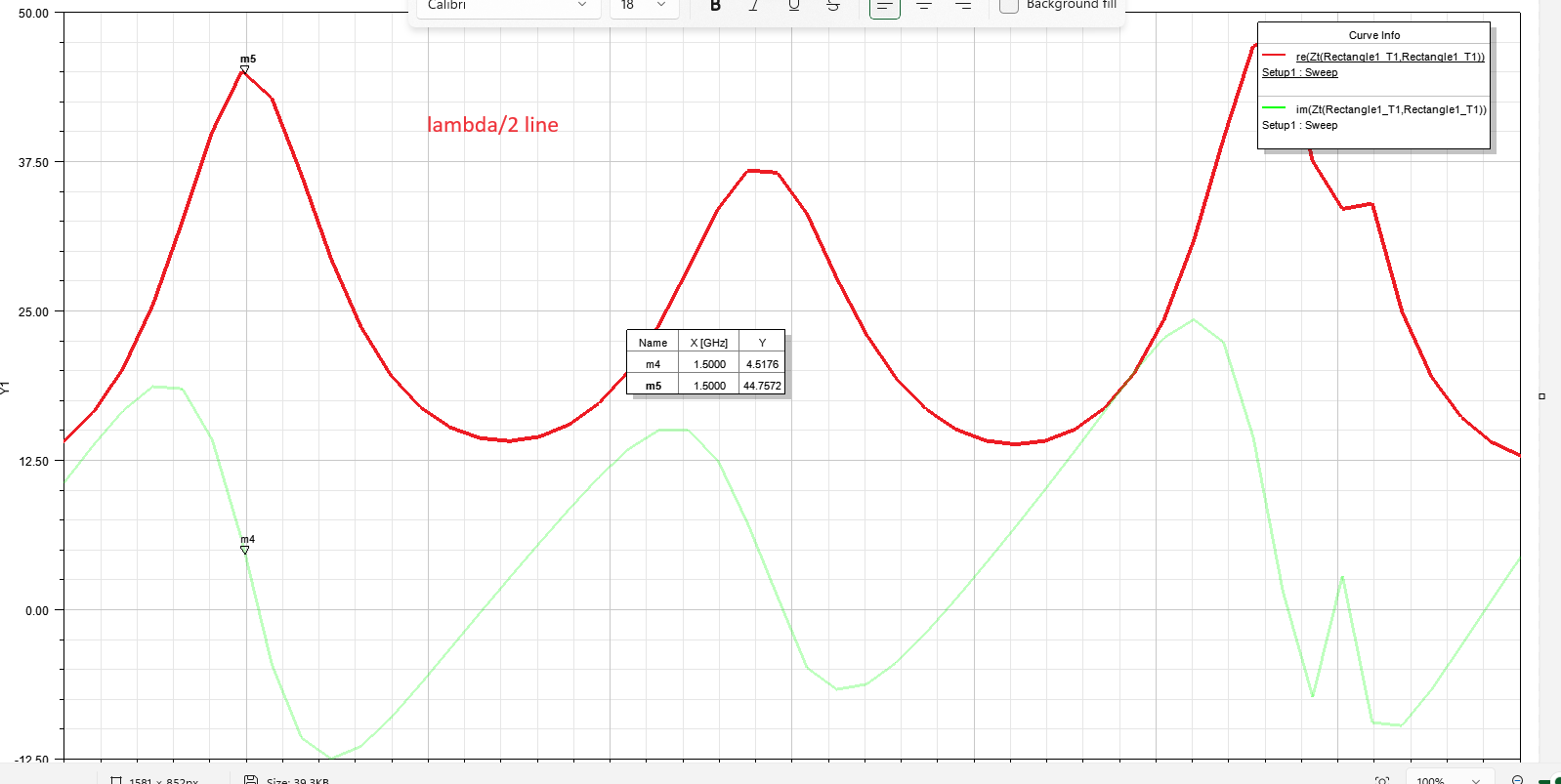

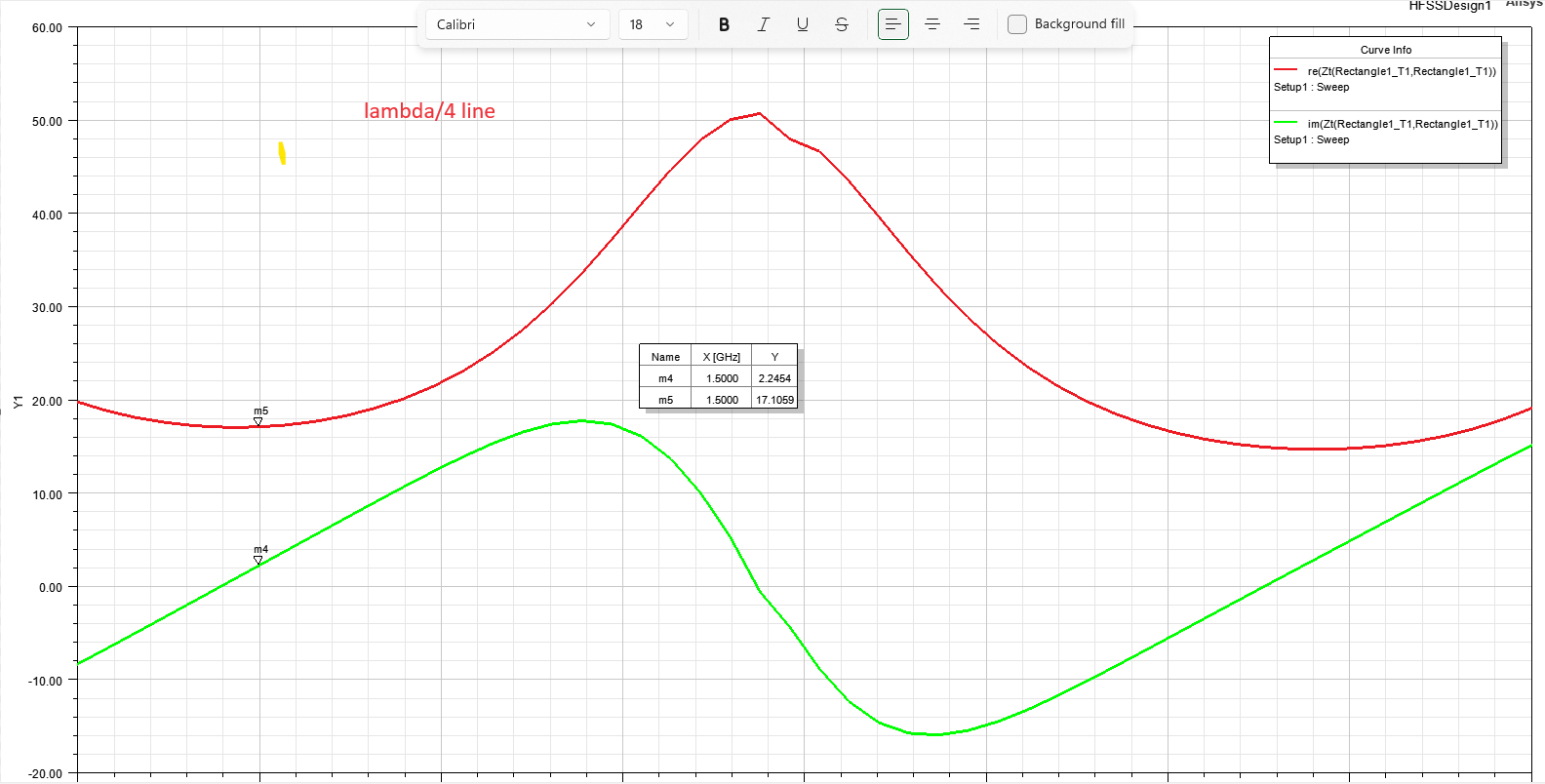

I am designing single port (50 ohms) coplanar waveguide of 50 ohms in HFSS which is connected to other end with 50 ohm lumped RLC component. The width and spacing of the waveguide is 0.412733mm and 0.05mm respectively in FR4_epoxy substrate (er=4.4). Since characteristic impedance of CPW is Zo= 50 ohm which is connected to load of ZA=50 ohm, using the following below relation, Zin should be always 50 ohms irrespective of βL based on mathematics as numerator and denominator being same. Thus, it should be same for all frequencies and all βL. I tried for lambda/2 and lambda/4 length (calculated using ADS linecalc for 1.5GHz) for 1 to 5GHz but could not achieve the constant 50 ohm input impedance for all frequencies or at 1.5GHz for two different length. I highly appreciate the help on this how to achieve my requirement. The design and simulation result are attached below.

I am designing single port (50 ohms) coplanar waveguide of 50 ohms in HFSS which is connected to other end with 50 ohm lumped RLC component. The width and spacing of the waveguide is 0.412733mm and 0.05mm respectively in FR4_epoxy substrate (er=4.4). Since characteristic impedance of CPW is Zo= 50 ohm which is connected to load of ZA=50 ohm, using the following below relation, Zin should be always 50 ohms irrespective of βL based on mathematics as numerator and denominator being same. Thus, it should be same for all frequencies and all βL. I tried for lambda/2 and lambda/4 length (calculated using ADS linecalc for 1.5GHz) for 1 to 5GHz but could not achieve the constant 50 ohm input impedance for all frequencies or at 1.5GHz for two different length. I highly appreciate the help on this how to achieve my requirement. The design and simulation result are attached below.