titophe

Newbie level 4

Hello,

I have a question relating to STA (Static Timing Analysis).

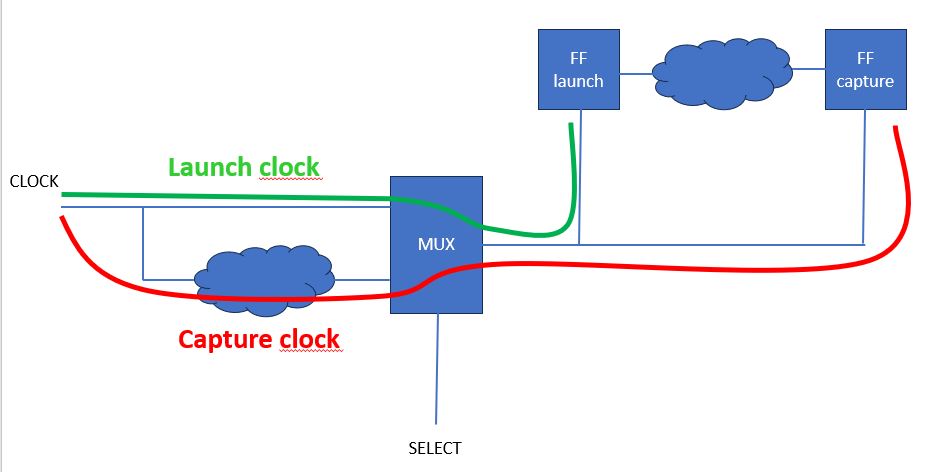

My design contains a MUX2:1 in its clock tree (cf. file attached).

I'm using Primetime from Synopsys for STA analysis.

In Primetime the timing report for hold check uses the "green" path for the launch clock and the "red" path for the capture clock.

To me this is pessimistic and unrealistic (As you know, for hold check, the same clock slope is used for launch and capture. In the real world the same clock slope can't go through the 2 input pins of the MUX at the same time and so the report is incorrectly pessimistic).

When I discuss this point with Synopsys, their answer is that it is a normal behaviour for an STA tool.

I'm wondering if someone could let me know if the other STA tools have the same behaviour (for example with Cadence Tempus).

Thanks in advance for your help

BR

cricri

I have a question relating to STA (Static Timing Analysis).

My design contains a MUX2:1 in its clock tree (cf. file attached).

I'm using Primetime from Synopsys for STA analysis.

In Primetime the timing report for hold check uses the "green" path for the launch clock and the "red" path for the capture clock.

To me this is pessimistic and unrealistic (As you know, for hold check, the same clock slope is used for launch and capture. In the real world the same clock slope can't go through the 2 input pins of the MUX at the same time and so the report is incorrectly pessimistic).

When I discuss this point with Synopsys, their answer is that it is a normal behaviour for an STA tool.

I'm wondering if someone could let me know if the other STA tools have the same behaviour (for example with Cadence Tempus).

Thanks in advance for your help

BR

cricri