cupoftea

Advanced Member level 6

Hi,

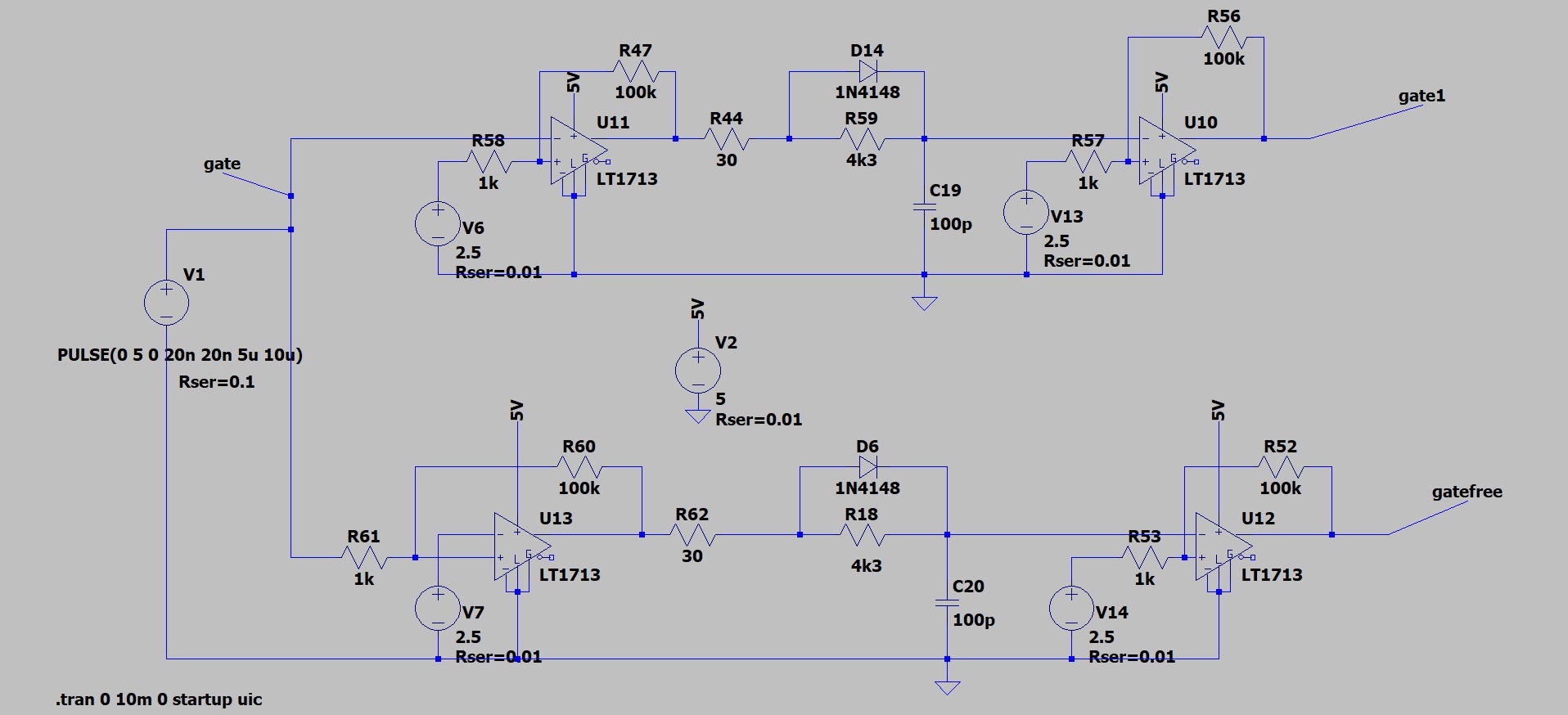

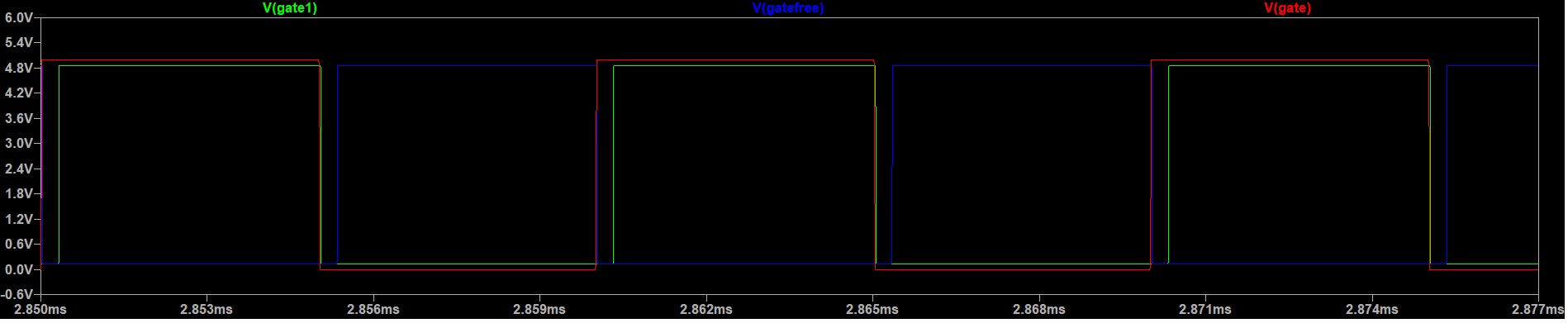

We have the following circuit in hardware....it receives the "gate" signal (shown in red), and then produces the other two pulse trains which are an anti-phase pulse train, sync'd by "gate"....but delayed from "gate" by about 300ns or so. (as can be seen). Please note the "dead" time in the waveforms

The "gate" signal is 100kHz. It has a duty cycle which varies between 0% and 50%.

Is there a particular cheap micro which is good for doing this?, ie, receiving "gate" , and then outputting the other 2 pulse trains?

What minimum frequency would the micro need to be at?

(schem, waveforms, and the LTspice sim of the hardware is as attached, please may you find it)

We have the following circuit in hardware....it receives the "gate" signal (shown in red), and then produces the other two pulse trains which are an anti-phase pulse train, sync'd by "gate"....but delayed from "gate" by about 300ns or so. (as can be seen). Please note the "dead" time in the waveforms

The "gate" signal is 100kHz. It has a duty cycle which varies between 0% and 50%.

Is there a particular cheap micro which is good for doing this?, ie, receiving "gate" , and then outputting the other 2 pulse trains?

What minimum frequency would the micro need to be at?

(schem, waveforms, and the LTspice sim of the hardware is as attached, please may you find it)