keyboardcowboy

Member level 3

When the signal level rises above a certain high threshold, the system switches to a high state, and when the signal falls below a certain low threshold, the system switches to a low state. The key point is that the high and low thresholds are not the same – there's a region of uncertainty between them. This is the hysteresis.

Does SDHC/eMMC standard requires an input hysteresis at the IO-cells?.

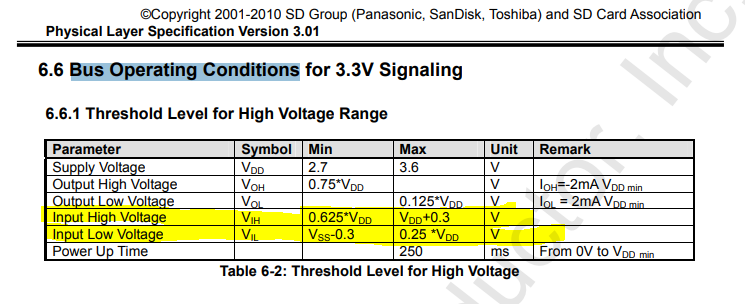

I was looking at the SD Specifications Part 1 Physical Layer, and found this table

If input high is 1.6875v (0.625x2.7) and input low is -0.3v then does that mean the hysterisis is 1.6875- (-0.3)

Does SDHC/eMMC standard requires an input hysteresis at the IO-cells?.

I was looking at the SD Specifications Part 1 Physical Layer, and found this table

If input high is 1.6875v (0.625x2.7) and input low is -0.3v then does that mean the hysterisis is 1.6875- (-0.3)