cupoftea

Advanced Member level 6

Hi,

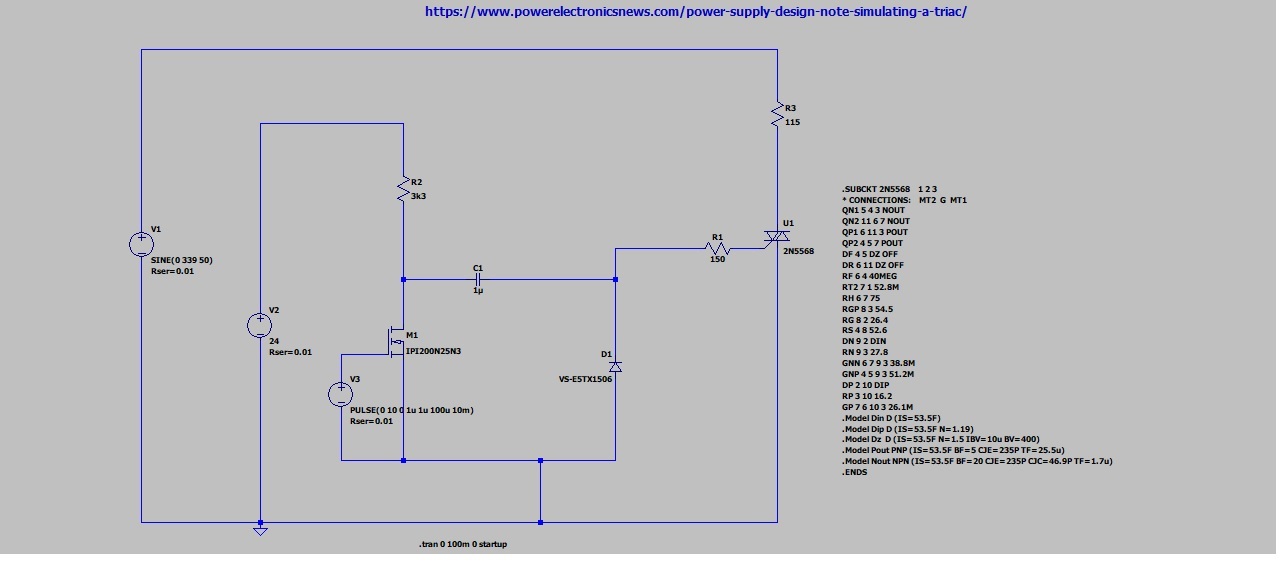

Do you know why this triac model doesnt work in LTspice.

I got it here.

https://www.powerelectronicsnews.com/power-supply-design-note-simulating-a-triac/

Do you know why this triac model doesnt work in LTspice.

I got it here.

https://www.powerelectronicsnews.com/power-supply-design-note-simulating-a-triac/