cupoftea

Advanced Member level 6

Hi,

There is a rule that Current Mode Half Bridge (HB) converters dont work due to rail splitting capacitor imbalance.

This is true where "pure" current mode is concerned (ie with no added slope on the current sense input), and even the LTspice simulator shows this.

However, as long as a Current Mode Half Bridge converter has some added slope then its fine.

AYK, obviously sub-harmonic oscillation would cause rail capacitor unbalance.

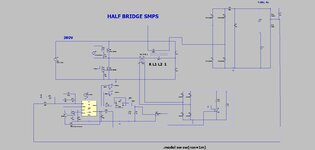

The attached is a current mode Half Bridge (LTspice and jpeg) with a 0.7 Duty cycle, and added slope compensation to keep it from sub-harmonic oscillation. It is even hacked so that its peak current is significantly different for every other switching cycle, and yet the rail capacitor unbalance produced is insignificant. (!!!)

Most Half Bridge converters are going to have added slope anyway due to the magnetising current.

As such, it is believed that Current Mode Half Bridges (with added slope) are actually fine after all.

The things that make sub-harmonic oscillation worse also seem to increase rail capacitor unbalance....eg if the inductor di is high, then it tends toward greater capacitor unbalance.

Is it the vendors of LLC chips that are cranking up the slating of the Half Bridge?.....because there seems to be no "official" text claiming that Half Bridge in Slope-added-Current-Mode is bad.

Neither Basso, Morey , Billings, Cuk, Musk, Mammano or Ridley say anything of it.

I believe that the problem of capacitor unbalancing with Half Bridge is no worse a threat than that of Severe reverse recovery in the LLC....in fact, HB is safer because you can overcome cap unbalance (mitigate damage) by just rating the caps for the full rail voltage.

(by LLC i mean LLC without series diode and without added software to prevent rev rec ever happening)

I believe LLC (with proviso) is worse than HB in respect of possible danger....what we are seeing is a "hit" on the plain HB by LLC chip vendors.

Pull out your current mode HB design spreadsheet and enjoy that half voltage rail input, and the lesser dv/dt that results....and the two FETs that are easy to bootstrap drive.

There is a rule that Current Mode Half Bridge (HB) converters dont work due to rail splitting capacitor imbalance.

This is true where "pure" current mode is concerned (ie with no added slope on the current sense input), and even the LTspice simulator shows this.

However, as long as a Current Mode Half Bridge converter has some added slope then its fine.

AYK, obviously sub-harmonic oscillation would cause rail capacitor unbalance.

The attached is a current mode Half Bridge (LTspice and jpeg) with a 0.7 Duty cycle, and added slope compensation to keep it from sub-harmonic oscillation. It is even hacked so that its peak current is significantly different for every other switching cycle, and yet the rail capacitor unbalance produced is insignificant. (!!!)

Most Half Bridge converters are going to have added slope anyway due to the magnetising current.

As such, it is believed that Current Mode Half Bridges (with added slope) are actually fine after all.

The things that make sub-harmonic oscillation worse also seem to increase rail capacitor unbalance....eg if the inductor di is high, then it tends toward greater capacitor unbalance.

Is it the vendors of LLC chips that are cranking up the slating of the Half Bridge?.....because there seems to be no "official" text claiming that Half Bridge in Slope-added-Current-Mode is bad.

Neither Basso, Morey , Billings, Cuk, Musk, Mammano or Ridley say anything of it.

I believe that the problem of capacitor unbalancing with Half Bridge is no worse a threat than that of Severe reverse recovery in the LLC....in fact, HB is safer because you can overcome cap unbalance (mitigate damage) by just rating the caps for the full rail voltage.

(by LLC i mean LLC without series diode and without added software to prevent rev rec ever happening)

I believe LLC (with proviso) is worse than HB in respect of possible danger....what we are seeing is a "hit" on the plain HB by LLC chip vendors.

Pull out your current mode HB design spreadsheet and enjoy that half voltage rail input, and the lesser dv/dt that results....and the two FETs that are easy to bootstrap drive.

Attachments

Last edited: