shashi123

Newbie

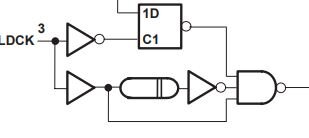

In datasheet SN74ALS232B by TI, there is this elliptical symbol with two lines inside can you please tell me what it is?

On page number 3 [logic diagram] Check the signal LDCK from there you can see the buffer below it and to it, an "elliptical symbol with two lines inside" (attached the image) is connected. please let me know what is this symbol means.

Please find the attachment for the symbol and circuit.

On page number 3 [logic diagram] Check the signal LDCK from there you can see the buffer below it and to it, an "elliptical symbol with two lines inside" (attached the image) is connected. please let me know what is this symbol means.

Please find the attachment for the symbol and circuit.