True koke

Newbie level 6

Hi. I am a beginner at ADS Momentum.

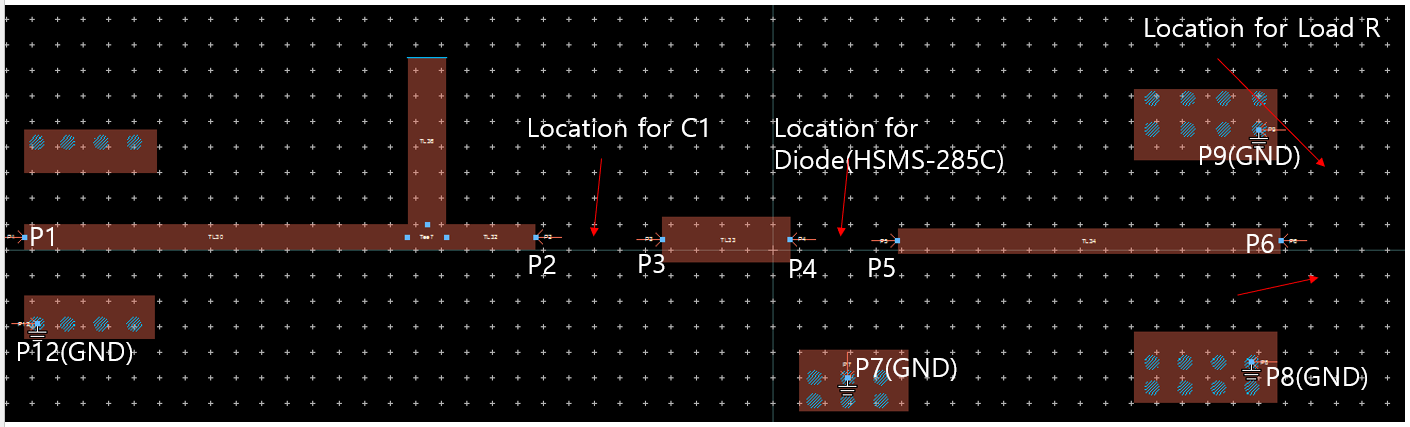

I have designed the rectifier using HSMS285C schottky diode.

I also designed layout the rectifier only using TL, but I don't know how to connect the Lumped elements and Diode in ADS circuit and how to setup the port.

My simulation step is like :

1. Sketch the circuit on Layout without any C,Diode,R....

-Because ADS EM simulation does not support Capacitor, R, Diode...

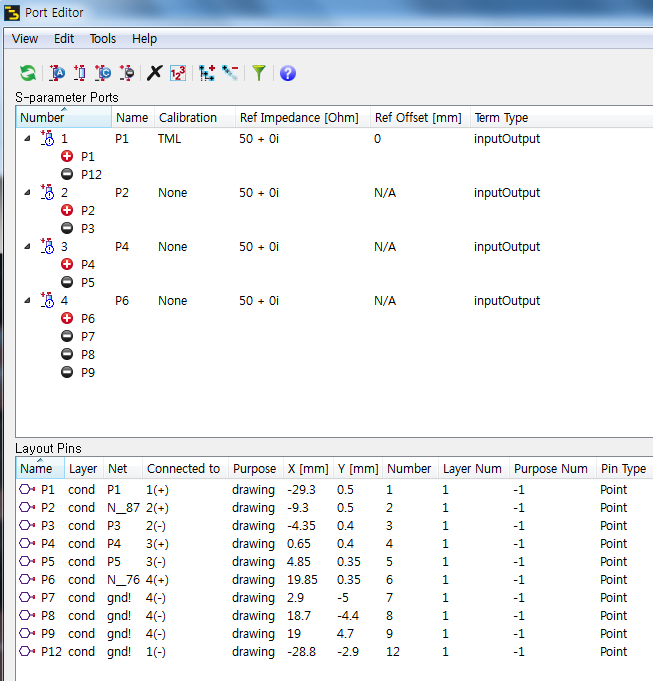

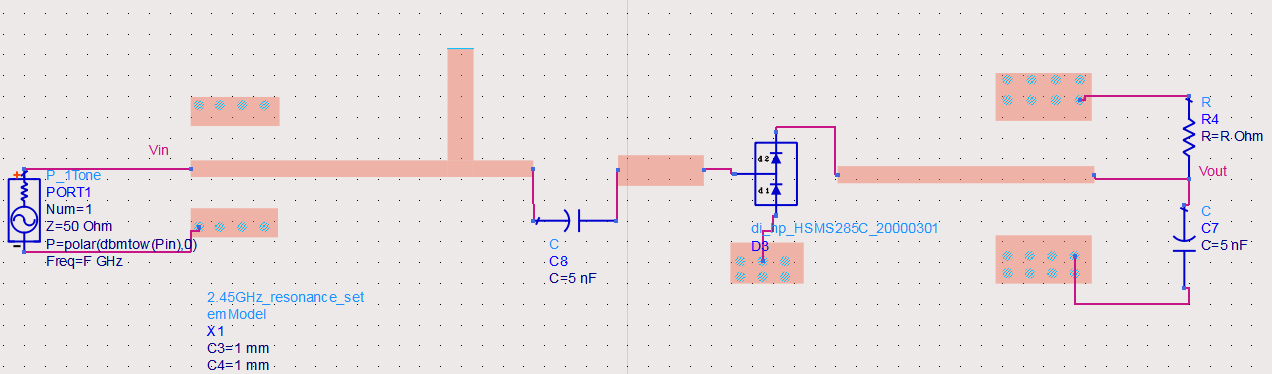

2. I made the Symbol to import to in my circuit.

3. I connected the C,R,Diode with my Symbol.

Please give me advice how to set the port(like Cal. type and connection each other ports to flow the current well..)

Please refer to the attched image.

I have designed the rectifier using HSMS285C schottky diode.

I also designed layout the rectifier only using TL, but I don't know how to connect the Lumped elements and Diode in ADS circuit and how to setup the port.

My simulation step is like :

1. Sketch the circuit on Layout without any C,Diode,R....

-Because ADS EM simulation does not support Capacitor, R, Diode...

2. I made the Symbol to import to in my circuit.

3. I connected the C,R,Diode with my Symbol.

Please give me advice how to set the port(like Cal. type and connection each other ports to flow the current well..)

Please refer to the attched image.