mtwieg

Advanced Member level 6

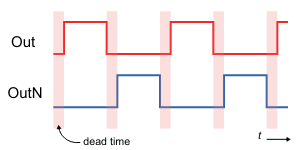

In a design I'm working on, I have two PWM signals generated by a switchmode power supply controller. The two signals are "mostly" complementary with a small amount of dead time tdead inserted where both signals must be low. For my application, tdead is around 5ns.

I want to use an FPGA to gate both these signals, but want to ensure skew is limited so tdead is not significantly altered.

I'm fairly new to SDC. I am aware of the set_max_skew command, but all the guidance I see on its usage refer to clocks or signals launched by clocks, whereas in my case my signals are totally asynchronous. And I want to consider skew all the way from the input pin to the output pin (including io delays), but most of the examples only consider pins to registers, or registers to pins.

The example I've found that seems most relevant is this:

But I don't really see how to adopt this to my needs. Let's assume my code looks like this:

So I want to constrain skew between the in > out paths (skew from the pwm_en signal isn't a concern).

I want to use an FPGA to gate both these signals, but want to ensure skew is limited so tdead is not significantly altered.

I'm fairly new to SDC. I am aware of the set_max_skew command, but all the guidance I see on its usage refer to clocks or signals launched by clocks, whereas in my case my signals are totally asynchronous. And I want to consider skew all the way from the input pin to the output pin (including io delays), but most of the examples only consider pins to registers, or registers to pins.

The example I've found that seems most relevant is this:

# Create a max skew constraint that includes input and output delays

# as well as the default data arrivals, clock arrivals and clock uncertainty

set_max_skew -from [get_keepers inst1|*] -to [get_keepers inst2|*] 0.200 \

-include { input_delay output_delay }

But I don't really see how to adopt this to my needs. Let's assume my code looks like this:

Code:

entity pwm_example is

port (

pwmA_in : in std_logic;

pwmB_in : in std_logic;

pwmA_out : out std_logic;

pwmB_out : out std_logic;

pwm_en : in std_logic

);

end pwm_example;

architecture rtl of pwm_example is

-- no declarations!

begin

pwmA_out <= pwmA_in when (pwm_en='1') else '0';

pwmB_out <= pwmB_in when (pwm_en='1') else '0';

end rtl;So I want to constrain skew between the in > out paths (skew from the pwm_en signal isn't a concern).

Last edited: