Manikumar_s

Newbie

Converter : Half Bridge LLC Resonance Converter

Transformer: Turns ratio: 5:1 (pry turns: sec turns)

PSU gain : Resonant gain X Converter Gain X Transformer gain.

LLC Converter operates on Inductive region above resonance condition for all load condition to achieve ZVS.

Max resonant gain in this condition 1.

Converter gain for Half bridge LLC is 1/2 and full bridge was 1.

Transformer gain was 1/5. And I am operating with 50% fixed Duty cyle and Max switching freq of 1000KHz to min freq of 600KHZ.

For the above specification, When I give input voltage of 270V, My output voltage should be =>Vin X Resonant gain (1) X Converter gain (1/2) X TRF Gain (1/5)

Output voltage => 270X1X1/2X1/5,

=> 270/10

=> 27V

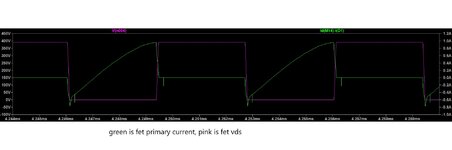

My Module output voltage should be 27V. But I am observing 28V output voltage for the 270V input at 30A output current (Converter operates in full load and Observed Switching freq was 690KHZ and my set Resonant freq was 480KHz)

Seems to be transformer gain was more than the estimated value. What may be reason for the above operation.

Transformer: Turns ratio: 5:1 (pry turns: sec turns)

PSU gain : Resonant gain X Converter Gain X Transformer gain.

LLC Converter operates on Inductive region above resonance condition for all load condition to achieve ZVS.

Max resonant gain in this condition 1.

Converter gain for Half bridge LLC is 1/2 and full bridge was 1.

Transformer gain was 1/5. And I am operating with 50% fixed Duty cyle and Max switching freq of 1000KHz to min freq of 600KHZ.

For the above specification, When I give input voltage of 270V, My output voltage should be =>Vin X Resonant gain (1) X Converter gain (1/2) X TRF Gain (1/5)

Output voltage => 270X1X1/2X1/5,

=> 270/10

=> 27V

My Module output voltage should be 27V. But I am observing 28V output voltage for the 270V input at 30A output current (Converter operates in full load and Observed Switching freq was 690KHZ and my set Resonant freq was 480KHz)

Seems to be transformer gain was more than the estimated value. What may be reason for the above operation.