jgk2004

Full Member level 5

- Joined

- Dec 1, 2009

- Messages

- 274

- Helped

- 77

- Reputation

- 154

- Reaction score

- 74

- Trophy points

- 1,308

- Location

- Munich Germany

- Activity points

- 3,520

Hello all,

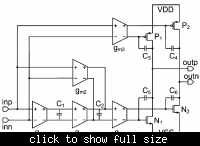

I am designing a 4 stage feedforward compensated amplifier and I am seeing a phase dip, see attached. I am wondering what people commonly consider reasonable dip when design 4 or higher stage amplifiers. Over all i am always above 40degrees. Also this amplifier will not be used as a follower but as an integrator, so i feel i shouldn't have a probem with instability.. What do you guys think?

Jgk

I am designing a 4 stage feedforward compensated amplifier and I am seeing a phase dip, see attached. I am wondering what people commonly consider reasonable dip when design 4 or higher stage amplifiers. Over all i am always above 40degrees. Also this amplifier will not be used as a follower but as an integrator, so i feel i shouldn't have a probem with instability.. What do you guys think?

Jgk