tahir4awan

Full Member level 4

Hallo,

I am building a project on Proteus. It is a LED chaser with 555 and 4017. The Problem is, in Simulator voltages are totally different. For example if I check output voltage of 555, it says 5V. But I have read Datasheet in which Output voltage is 3.3V. If I connect Output of 555 to Input CLK Pin of 4017 in Simulator it will Work fine. But If I use Manual Signal of 3.3v to Input CLK pinof 4017 in Simulator it will not Work.

I have searched, but could not able to find, that how much voltage and current need for an Input CLK of digital ICs.

Secondly can I connect Output Signal of 4017 directly to a Flip Flop. Because in Simulator Output voltage is again 5V. But I am not sure about current ranges. Do I need Transistors to ampilfy current?

Thanks

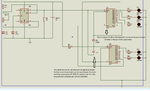

This is the Project. Instead of Leds output from 4017, I want to use Latch Flip Flops and then Leds.

I am building a project on Proteus. It is a LED chaser with 555 and 4017. The Problem is, in Simulator voltages are totally different. For example if I check output voltage of 555, it says 5V. But I have read Datasheet in which Output voltage is 3.3V. If I connect Output of 555 to Input CLK Pin of 4017 in Simulator it will Work fine. But If I use Manual Signal of 3.3v to Input CLK pinof 4017 in Simulator it will not Work.

I have searched, but could not able to find, that how much voltage and current need for an Input CLK of digital ICs.

Secondly can I connect Output Signal of 4017 directly to a Flip Flop. Because in Simulator Output voltage is again 5V. But I am not sure about current ranges. Do I need Transistors to ampilfy current?

Thanks

--- Updated ---

This is the Project. Instead of Leds output from 4017, I want to use Latch Flip Flops and then Leds.

Attachments

Last edited: