komax

Junior Member level 3

Hey guys,

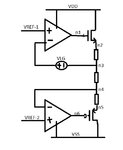

Please see the sketch of my circuit here.

I want to do loop-gain analysis (a.k.a. loop stability analysis) for the top loop. In simulation I simply put a voltage source (i.e. VLG) in part of the feedback and run the LG analysis (ie. AC loop gain).

My question is how to get my various poles and zeroes when I have multiple feedback loop? Note I'm not asking from simulation point of view but rather from analysis, let's say I need to derive the poles and zeros.

If n4 (node-4) is ground/VSS then this is a simple 1-loop system where my first pole will be at n1 (most likely dominant) and second pole at n2 and that's that. With additional loop at the bottom, I would think that my small signals from VLG will also travel to the bottom loop and thus affecting the overall response. How do I derive the combined transfer function for multiple loop such as this?

My simulation shows a zero appearing but I have no idea where from.

Thank you in advance for all your responses. Have a great day!

Please see the sketch of my circuit here.

I want to do loop-gain analysis (a.k.a. loop stability analysis) for the top loop. In simulation I simply put a voltage source (i.e. VLG) in part of the feedback and run the LG analysis (ie. AC loop gain).

My question is how to get my various poles and zeroes when I have multiple feedback loop? Note I'm not asking from simulation point of view but rather from analysis, let's say I need to derive the poles and zeros.

If n4 (node-4) is ground/VSS then this is a simple 1-loop system where my first pole will be at n1 (most likely dominant) and second pole at n2 and that's that. With additional loop at the bottom, I would think that my small signals from VLG will also travel to the bottom loop and thus affecting the overall response. How do I derive the combined transfer function for multiple loop such as this?

My simulation shows a zero appearing but I have no idea where from.

Thank you in advance for all your responses. Have a great day!

Last edited by a moderator: