spswaroopa

Newbie level 4

Hi,

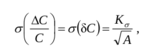

I am designing a 12 bit SAR ADC, for that I need to select minimum unit capacitor for the DAC, And I am using sqrt(KT/C)< LSB/2 formula to calculate the capacitor value. The obtained capacitor value minimises the thermal noise impact, what about the other parameters like mismatch etc. and how they affects the capacitor value? How to select the capacitor value over these effects? or how to overcome from these effects?

Is there any formula to calculate effective minimum capacitor value?

please help me to find answer.

I am designing a 12 bit SAR ADC, for that I need to select minimum unit capacitor for the DAC, And I am using sqrt(KT/C)< LSB/2 formula to calculate the capacitor value. The obtained capacitor value minimises the thermal noise impact, what about the other parameters like mismatch etc. and how they affects the capacitor value? How to select the capacitor value over these effects? or how to overcome from these effects?

Is there any formula to calculate effective minimum capacitor value?

please help me to find answer.