nihan_A

Newbie level 5

Hello everyone!

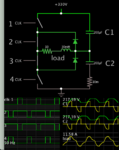

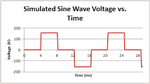

I am trying to remake an inverter which previously designed with IPM. I redesign it with mosfets instead of IPM and I use push-pull topology. I change PWM pulse width while reading the input voltage of the inverter (Such as if input voltage is 60V mosfet is on for 3.5msn-this is minimum pulse- if voltage is lower than 60V pulse increase up to 9msn). Actually I think there is nothing wrong with PWM since if there is load at the ouput there is no problem at all. But if there is no load at the output of inverter my sinewave is not as expected as you can see below

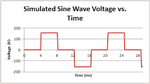

But it should be like this:

It seems like something acts like a capacitor when both of the mosfets are off state. But I don't have any idea.

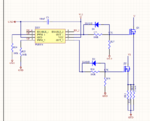

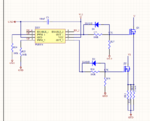

Here is my schematic

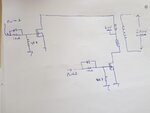

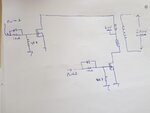

The U and V points are connected to transformer and center of the transformer is connected to 60V battery as you can see below

I am waiting for you replies.

I am trying to remake an inverter which previously designed with IPM. I redesign it with mosfets instead of IPM and I use push-pull topology. I change PWM pulse width while reading the input voltage of the inverter (Such as if input voltage is 60V mosfet is on for 3.5msn-this is minimum pulse- if voltage is lower than 60V pulse increase up to 9msn). Actually I think there is nothing wrong with PWM since if there is load at the ouput there is no problem at all. But if there is no load at the output of inverter my sinewave is not as expected as you can see below

But it should be like this:

It seems like something acts like a capacitor when both of the mosfets are off state. But I don't have any idea.

Here is my schematic

The U and V points are connected to transformer and center of the transformer is connected to 60V battery as you can see below

I am waiting for you replies.