Antra_Saxena

Newbie level 4

Hello,

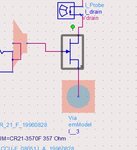

I am designing a PA using Cree transistor.

When I am doing EM simulation, after optimization of full PA ( EM model), I am getting PAE of 67%. Then, I observed that I have ideal ground in EM simulation at the source of the transistor. When I replaced it with Via ground, after optimization I can achieve up to 55 % only.

I am not understanding, why one Via ground reduced my PAE drastically.

Is it necessary to have Via ground or ideal ground can work?

When soldering a Cree transistor, source need to be connected to ground, via ground is required?

Thanks in advance,

I am designing a PA using Cree transistor.

When I am doing EM simulation, after optimization of full PA ( EM model), I am getting PAE of 67%. Then, I observed that I have ideal ground in EM simulation at the source of the transistor. When I replaced it with Via ground, after optimization I can achieve up to 55 % only.

I am not understanding, why one Via ground reduced my PAE drastically.

Is it necessary to have Via ground or ideal ground can work?

When soldering a Cree transistor, source need to be connected to ground, via ground is required?

Thanks in advance,