Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

so if we have rams that can do read/write simultaneously, we should always use rams for fifo? Any other cons of using rams over fifo?

| Large | Small |

| poor | high |

| High | Low |

| Any voltage above Vth, can work with as low as 0.6V | Significantly higher than your nominal core voltage, typically 1.2-1.5V (+100% Vth) |

| Not needed | Requires level shifters for cross voltage signals due to the above point, and repeaters |

| Easy and automated | Custom and difficult |

| Cheap, can be designed internally | Expensive and requires royalty for every SRAM block used |

| Low, guaranteed by digital design, easy fix upon failure | High due to possibility to enter into metastable state, or write failure by picking up latchup event from radiation |

| Flexible | Restrictive, and comes in chunks. You need to further isolate the silicon area used with a buffer region for SRAM due to the higher voltage |

| Fast | Slow |

Let's get into context. For memory, we have a few solutions at hand to fulfill our need: SRAM cells, latches, or registers.

Basically, latches and registers are made up of multiple digital logics. Because they are CMOS structure, their gate output Vout is independent of input Vgs, The output voltage can essentially drive loads at about Vdd voltage (pros for registers).

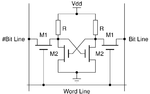

SRAMs are essentially 2 or 4 cells "holding" the voltage. They remember the signal by a feedback mechanism, as shown by the below image.

Because they are build with only a handful of transistors, SRAMs are more compact (pros for SRAM). This is in contrast of registers that are made of multiple logic gates (vastly more transistors).

Consisting only a handful of transistor, SRAMs are less power hungry and dissipates the least amount of power (pros of SRAM).

View attachment 150516

https://upload.wikimedia.org/wikipedia/commons/5/56/4T_SRAM_Cell.png

However, notice that SRAM output bitline has to go thru a level of resistance through resistor R and mosfet M1. There is also no PMOS+NMOS (CMOS) complementary benefit for M1 connected in series to the memory cell M2. Therefore, your SRAM bitline switches more slowly (cons of SRAM), and cannot drive bigger load, as the Vbitline = Vdd - (VR + Vm2 (cons of SRAM).

If Vbitline drops to a certain threshold, your memory cell cannot function. This is why SRAM usually operates at a voltage higher than your standard digital registers (cons of SRAM).

To help reduce voltage drop at R and M1, and to improve switching speed of bitline, SRAMs are designed in a custom manner with analog mathematics in consideration (cons of SRAM) instead of being digitally guaranteed signalling. Registers on the other hand have a guaranteed digital output and can be placed and routed in an automated fashion (pros of registers).

However, when designed in a custom manner, engineers can further increase the density of the transistors (pros of SRAM). Because of the heavy customization of the transistors, most companies find it better to just "buy" the SRAM (cons of SRAM) designs from reputable companies that have done enough research on the transistor node and with the best/densest SRAM implementation. So when the companies buys the SRAMs, they will usually buy the SRAM that has a big footprint, but with the densest amount of memory cells.

On the other hand, register banks are something that is pretty standardized based on your fab, and can be digitally placed and routed anywhere in you silicon (pros of registers), compared to bought SRAMs that come in "chunks".

To recap (but not exhaustively listed):

[td]Registers[/td]

Large Small poor high High Low Any voltage above Vth, can work with as low as 0.6V Significantly higher than your nominal core voltage, typically 1.2-1.5V (+100% Vth) Not needed Requires level shifters for cross voltage signals due to the above point, and repeaters Easy and automated Custom and difficult Cheap, can be designed internally Expensive and requires royalty for every SRAM block used Low, guaranteed by digital design, easy fix upon failure High due to possibility to enter into metastable state, or write failure by picking up latchup event from radiation Flexible Restrictive, and comes in chunks. You need to further isolate the silicon area used with a buffer region for SRAM due to the higher voltage Fast Slow

[td]Pros/Cons[/td]

[td]SRAMs[/td] [td]Silicon area cost[/td]

[td]Memory Density[/td]

[td]Power Consumption[/td]

[td]Operating Voltage[/td]

[td]Requirement for Supplementary Logics[/td]

[td]Design Complexity[/td]

[td]Design Cost[/td]

[td]Potential for failure/metastability[/td]

[td]Placement in silicon[/td]

[td]Responsiveness[/td]

All in all, silicon area cost and power consumption trumps all others, hence for architectures where memory banks are less referenced (low read/write op, non-speed critical), SRAMs are generally preferred.