righteous

Full Member level 2

Dear Engineers (both pro and amateurs),

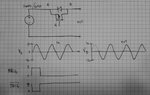

I would be grateful if someone could throw me a bone here, a general idea of the direction would suffice, on how to make a fast analog switch that will do the following:

My challenge is to make an analog switch that is open during the first positive (half) period of PULSE. I'm personally thinking along the lines of a thyristor here...

I don't know much about the voltage source at this point, but it can also source current, 20-40mA would be a good guesstimate, and I would like to pass both voltage and current through the switch.

BTW: I also have access to the timing signal (both INV and non-INV) that triggers the pulse, it's a CMOS output and is aprox. 100ns wide.

I would be grateful if someone could throw me a bone here, a general idea of the direction would suffice, on how to make a fast analog switch that will do the following:

My challenge is to make an analog switch that is open during the first positive (half) period of PULSE. I'm personally thinking along the lines of a thyristor here...

I don't know much about the voltage source at this point, but it can also source current, 20-40mA would be a good guesstimate, and I would like to pass both voltage and current through the switch.

BTW: I also have access to the timing signal (both INV and non-INV) that triggers the pulse, it's a CMOS output and is aprox. 100ns wide.

Last edited: