Jester

Full Member level 6

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You'll need to change the load resistor, and maybe your scaling resistors. And make sure your FETS can handle the current and power. You may need to dissipate a LOT of power, depending on how you set this up.

very little extra voltage is required to drive significantly more current so the voltage DRV (gate) signal has to be non-linear to give a linear output current. Does that make sense or am I out in left field with my interpretation?

In addition possibly a series resistor to C5 to increase the phase margin (turning a pure I controller into PI).I'd add an R between R4 and C5. Then lower C5.

This makes it more easy for the Opamp to drive the Output.

More precise because faster regulation, less ringing.

Hi,

I'd add an R between R4 and C5. Then lower C5.

This makes it more easy for the Opamp to drive the Output.

More precise because faster regulation, less ringing.

Klaus

Hi,

1k, 15nF (gives an fc of about 10kHz. Modify according your taste)

Klaus

Next step is to see if I can get this to work at significantly higher voltage and current.

If I'm interpreting the SOA curve correctly it looks like I might squeeze about 20A@24Vac, 1.75A@120Vac, 240vac looks marginal even at 100mA, does that look correct?

https://ixapps.ixys.com/DataSheet/DS99990(IXTK-TX32P60P).pdf

IF I place a diode is parallel with the body diode so that each FET is only conducting current 1/2 the time (assuming the external diode has a lower Vf) could I perhaps squeeze a bit more current from these FET's?

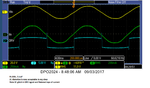

If you want the zero cross to improve, you should consider lower value capacitors instead of higher value capacitors.With 1k, 15nF the system is stable, however the zero-cross drop out is quite significant, however with a 30nF and lower R, I tried 470r, and 220r the ZC glitches are almost acceptable

It seems there might be some value in trying to bias the gates of the two fets such that when the opamp is outputting zero both gates are biased towards their on threshold (just below it). I.E. pull the gate of the N up and the gate of the P down. The goal is to minimize the op-amp's jump at crossover. Though adding R to create this network would compromise bandwidth. Zeners would work for this too. Though it will never be perfect because the thresholds vary too much (between devices and over temperature).