T

treez

Guest

Hello,

We have to do a non-isolated SMPS for vin=120v to 400v, and vout = 100v, pout=300w.

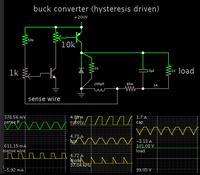

There is a “known” way to do this involving two cascaded synchronous buck stages. The upstream stage works either in DCM or in resonant mode so as to provide a lower voltage bus for the downstream buck, so that the downstream buck suffers less switching loss.

The upstream buck stage suffers low switching loss due to being in either resonant mode or in DCM (zero fet current at turn on).

Both buck hi-side fets are literally driven from the same output of a single current mode controller (eg ucc28c4x series). Current sense transformers and high side gate drive transformers thrown in as required. Only the output of the downstream buck is regulated.

Do you know more detail of this “known” method?

We have to do a non-isolated SMPS for vin=120v to 400v, and vout = 100v, pout=300w.

There is a “known” way to do this involving two cascaded synchronous buck stages. The upstream stage works either in DCM or in resonant mode so as to provide a lower voltage bus for the downstream buck, so that the downstream buck suffers less switching loss.

The upstream buck stage suffers low switching loss due to being in either resonant mode or in DCM (zero fet current at turn on).

Both buck hi-side fets are literally driven from the same output of a single current mode controller (eg ucc28c4x series). Current sense transformers and high side gate drive transformers thrown in as required. Only the output of the downstream buck is regulated.

Do you know more detail of this “known” method?