sunidrak

Full Member level 1

- Joined

- Apr 12, 2012

- Messages

- 97

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,288

- Location

- Bengaluru, India

- Activity points

- 1,738

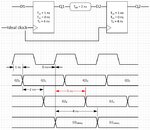

Why the maximum frequency of operation of Sequential design doesn't depend upon Hold time of a fliflop ??

plz reply

plz reply