franticEB

Full Member level 3

Hi,

i'm testing a class d full bridge amplifier with a digital piloting of mos driver with pwm technique.

Dead times for mosfet are generated in digital way.

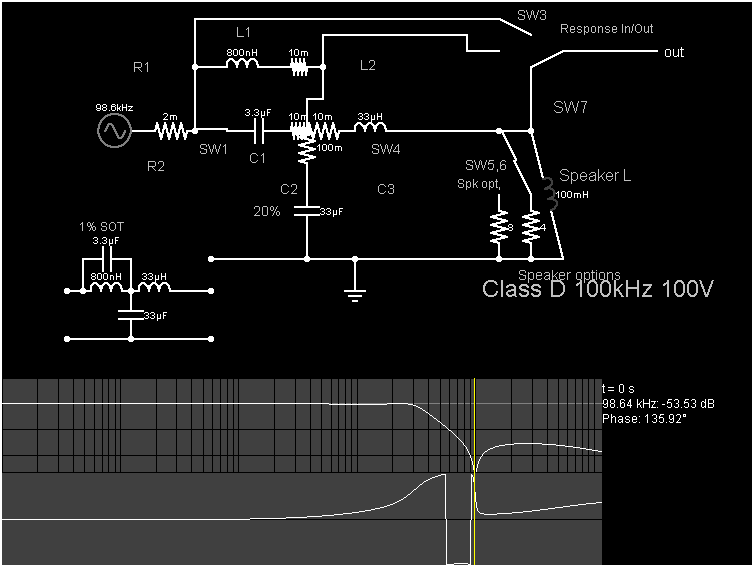

The circuit is in figure below

The aim is to generate a 5Khz sine wave. So the frequency of pwm is 200KHz.

The bridge doesn't work very well. The signal on the gate of the high side mosfet is very bad and presents a lot of spikes.

Have you have some advice to correct piloting the bridge and to modify the circuit in order to obtain the best performance?

Thanks

i'm testing a class d full bridge amplifier with a digital piloting of mos driver with pwm technique.

Dead times for mosfet are generated in digital way.

The circuit is in figure below

The aim is to generate a 5Khz sine wave. So the frequency of pwm is 200KHz.

The bridge doesn't work very well. The signal on the gate of the high side mosfet is very bad and presents a lot of spikes.

Have you have some advice to correct piloting the bridge and to modify the circuit in order to obtain the best performance?

Thanks