mpig09

Full Member level 4

Hi all:

There are two nmos models in the spice model : isolation nmos and normal nmos.

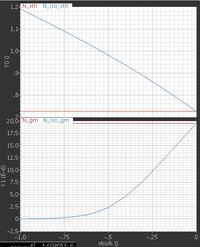

I simulate the i-v curve, and the result shows the curve are the same with isolation nmos and normal nmos.

Does anyone know the difference of application and layout between isolation nmos and normal nmos ?

Thanks for your view and reply.

mpig

There are two nmos models in the spice model : isolation nmos and normal nmos.

I simulate the i-v curve, and the result shows the curve are the same with isolation nmos and normal nmos.

Does anyone know the difference of application and layout between isolation nmos and normal nmos ?

Thanks for your view and reply.

mpig