Osawa_Odessa

Banned

- Joined

- Dec 31, 2012

- Messages

- 168

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,298

- Activity points

- 0

Hi,

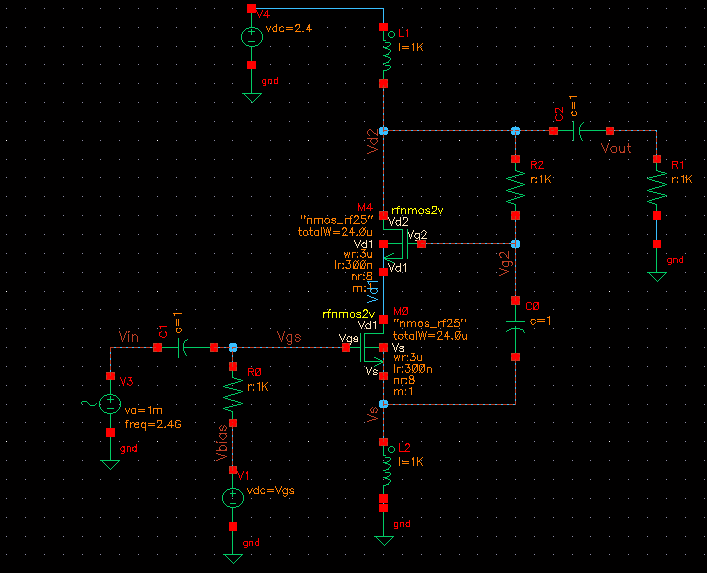

I am simulating RF self-biased cascode power amplifer in Cadence under the paper below:

A 2.4GHz, 0.18µm CMOS self-biased cascode power amplifier. (attached below)

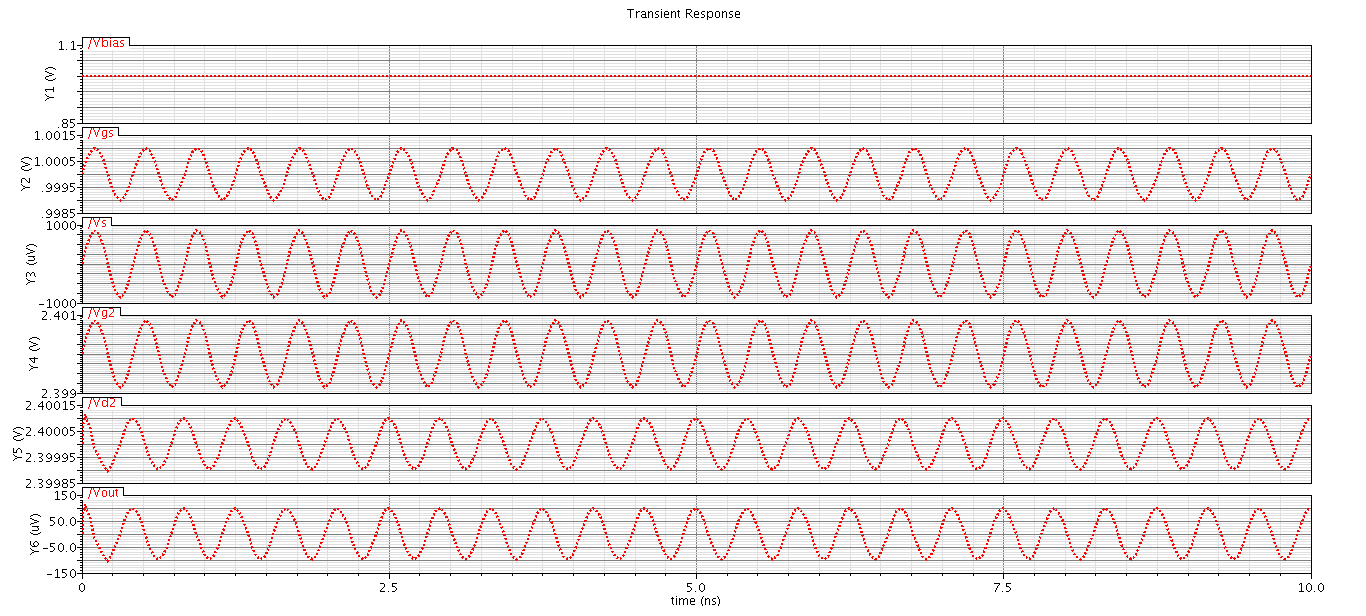

My problem is that the output voltage, Vout, is even smaller than input voltage, Vin. Meaning that it doesn't amply at all even attenuate input signal.

Could anyone help?

Here is the simulation schematic:

And this is waveforms at some important nodes:

And the paper:

I am simulating RF self-biased cascode power amplifer in Cadence under the paper below:

A 2.4GHz, 0.18µm CMOS self-biased cascode power amplifier. (attached below)

My problem is that the output voltage, Vout, is even smaller than input voltage, Vin. Meaning that it doesn't amply at all even attenuate input signal.

Could anyone help?

Here is the simulation schematic:

And this is waveforms at some important nodes:

And the paper: