ppinus

Newbie level 4

I need help to create a 3-bit Gray code counter that can count both forwards and backwards. Using flip-flops as memory, I was able to create a counter but only in one direction. The dir signal, despite changing, cannot reverse the counting direction. The flip-flop needs to have the same value as input to change the exit. I noticed that the counter counts only in the direction it is in at the time of the reset. When dir = 0 it should count from 0 to 7 and when dir = 1 from 7 to 0. I do not waant to change the flipflop.

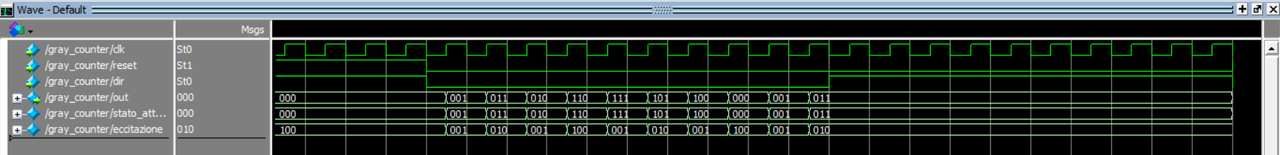

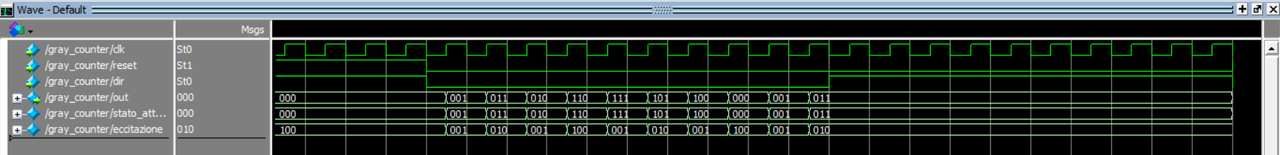

This is the simulation:

This is the verilog code:

This is the simulation:

This is the verilog code:

Code Verilog - [expand]

Last edited by a moderator: