samabraham

Newbie level 6

- Joined

- Mar 16, 2013

- Messages

- 12

- Helped

- 3

- Reputation

- 6

- Reaction score

- 3

- Trophy points

- 1,283

- Location

- Bangalore

- Activity points

- 1,359

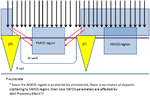

I have seen in PDKs spacing for NMOS from Nwell. Can anyone explain how an NMOS will get affected during Nwell fabrication??:!:

please help...

please help...

Last edited: