rf1008

Full Member level 2

- Joined

- Mar 30, 2012

- Messages

- 129

- Helped

- 7

- Reputation

- 14

- Reaction score

- 7

- Trophy points

- 1,298

- Activity points

- 2,219

Hello,

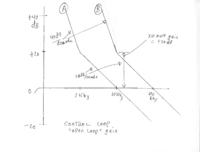

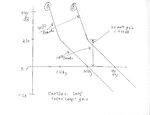

I use one PLL chip from ADI in my design and have a question on the charge pump current. Several current levels could be selected, from lower 0.6mA to higher 5mA. I verified and found that lower current will decrease the noise out-of band which seems to be better,I haven't found any performance deteriorated maybe due to my incompleted measurement.

Would you pls advise how to choose the charge pump current ,the lower the better or....thanks.

I use one PLL chip from ADI in my design and have a question on the charge pump current. Several current levels could be selected, from lower 0.6mA to higher 5mA. I verified and found that lower current will decrease the noise out-of band which seems to be better,I haven't found any performance deteriorated maybe due to my incompleted measurement.

Would you pls advise how to choose the charge pump current ,the lower the better or....thanks.