jasonc2

Full Member level 4

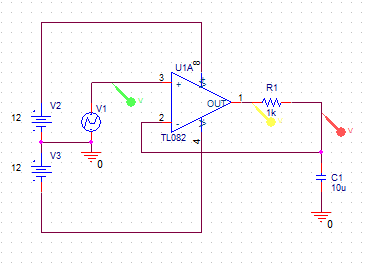

When I use an op amp to charge a capacitor through a resistor (even just the op amps output resistance), sensing the capacitor voltage, it oscillates when it hits the target voltage (as expected since its a low pass filter), e.g. https://www.falstad.com/circuit/#$+...+448+336+0

o+4+64+0+34+10.0+9.765625E-5+0+-1

.

Is there a way to reduce / eliminate this ringing?

Thanks!

Is there a way to reduce / eliminate this ringing?

Thanks!