cmos_ajay

Full Member level 2

Hello,

Attached is a picture of a opamp schematic.

It represents TEXAS Instruments op-amp OPA350 as seen in datasheet.

This opamp drives very high capacitive loads ( micro farads ) when connected as a unity gain buffer. It has gain > 100dB . The first stage is a standard folded cascode.

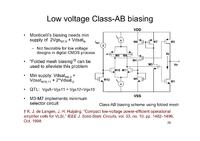

a] What do you think is the architecture of the class AB control circuitry seen in the picture ??

b] To drive high capacitive loads, the miller compensation will 'not' be useful at all

c] Is there any other opamp architecture to drive large capacitive load with high gain and bandwidth ??

Thanks.

Attached is a picture of a opamp schematic.

It represents TEXAS Instruments op-amp OPA350 as seen in datasheet.

This opamp drives very high capacitive loads ( micro farads ) when connected as a unity gain buffer. It has gain > 100dB . The first stage is a standard folded cascode.

a] What do you think is the architecture of the class AB control circuitry seen in the picture ??

b] To drive high capacitive loads, the miller compensation will 'not' be useful at all

c] Is there any other opamp architecture to drive large capacitive load with high gain and bandwidth ??

Thanks.