ducvilla

Member level 3

Hi! Can somebody help me!

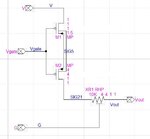

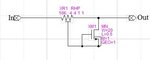

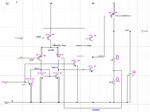

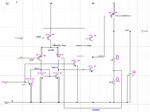

I am newbie on analog ic design. I have a problem with off-signal to shutdown the LDO circuit.

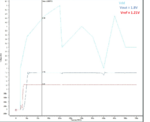

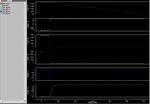

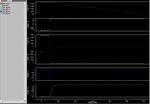

In my circuit, I think when Voff is high, then the transistor XM18 and XM19 is ON, then all other transistors is OFF, then the Vout should be 0V. But when i simulation, all are true except Vout is still high.

Firstly, i think because of charging of capacitor, but it is clear that the charging is only in instance.

Regard.

I am newbie on analog ic design. I have a problem with off-signal to shutdown the LDO circuit.

In my circuit, I think when Voff is high, then the transistor XM18 and XM19 is ON, then all other transistors is OFF, then the Vout should be 0V. But when i simulation, all are true except Vout is still high.

Firstly, i think because of charging of capacitor, but it is clear that the charging is only in instance.

Regard.