ffsher100

Junior Member level 3

- Joined

- Jun 16, 2011

- Messages

- 27

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Activity points

- 1,486

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

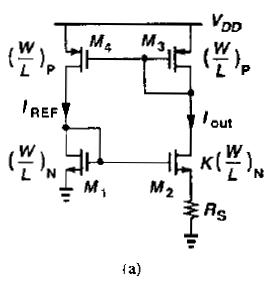

whether the circuit needn't start-up circuit?

As I told you in my first answer above: use the IC (Initial Condition) statement for the 2 gate nodes.... how to setup analysis condition to force degenerate point show up?