anand37

Newbie level 4

- Joined

- Jan 22, 2008

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,329

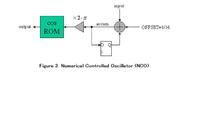

please can any one give me the vhdl codes for the phase accumulator and the LUT(look up table) required in a numerically controlled oscillator.