isaac12345

Member level 2

- Joined

- Mar 24, 2010

- Messages

- 47

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Activity points

- 1,634

Hi all!

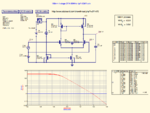

Been trying to design a differential amplifier with the following specifications(in cadence virtuoso) but been unsuccessful again and again. Given up! Can anyone give it a try and explain(with a schematic?). Would much appreciate it

Specs -

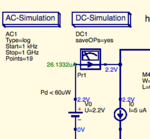

Av =>40db

Pd<100uW

Slew Rate=>20v/usec

CMRR=>50db

ICMR=0.8 to 3.0v

Gain Bandwidth product = 50MHz

Vout swing =0.7 to 1.5v

Assume load capacitance = 1pF, Vdd=2.2v, unCox=300u and upcox=50u

Been trying to design a differential amplifier with the following specifications(in cadence virtuoso) but been unsuccessful again and again. Given up! Can anyone give it a try and explain(with a schematic?). Would much appreciate it

Specs -

Av =>40db

Pd<100uW

Slew Rate=>20v/usec

CMRR=>50db

ICMR=0.8 to 3.0v

Gain Bandwidth product = 50MHz

Vout swing =0.7 to 1.5v

Assume load capacitance = 1pF, Vdd=2.2v, unCox=300u and upcox=50u