tenso

Advanced Member level 4

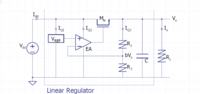

I have been trying to understand a series of equations I have come across. The equations deal with dropout voltage of a linear regulator with a NMOS pass device. Below is the schematic of the generic linear regulator.

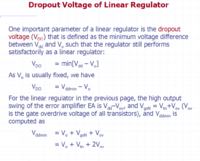

The second picture below has the slide which has the equations.

I get the first two equations that dropout voltage is equal to Vdd min (input voltage min) minus the output voltage Vo.

What I don't get is how for the third equation for Vdd min has the gate-source voltage of the NMOS pass device, VgsN. Shouldn't Vddmin just be Vov + Vo? Why care about the gate to source voltage drop?

The second picture below has the slide which has the equations.

I get the first two equations that dropout voltage is equal to Vdd min (input voltage min) minus the output voltage Vo.

What I don't get is how for the third equation for Vdd min has the gate-source voltage of the NMOS pass device, VgsN. Shouldn't Vddmin just be Vov + Vo? Why care about the gate to source voltage drop?

Last edited by a moderator: