allennlowaton

Full Member level 5

I did a post-simulation with my OP alone. I found out that there's a 20mV~30mV DC difference on its inputs. The gain is not anymore positive. Further simulation shows that the said OP can only afford to have 2mV DC difference on its inputs. How can I improved my OP to obtain such requirement?

---------- Post added at 09:34 ---------- Previous post was at 07:52 ----------

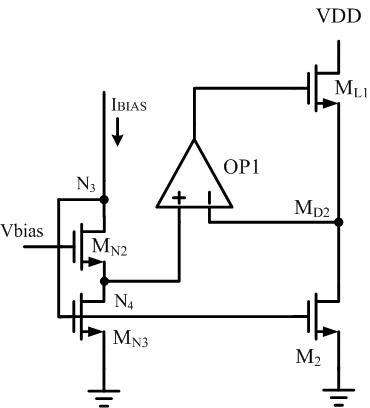

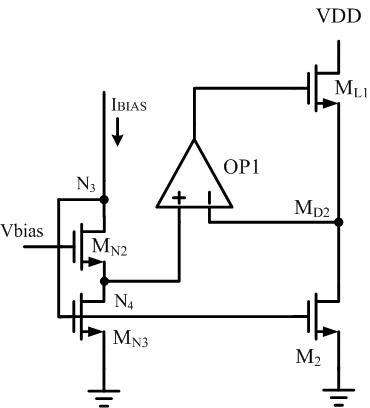

this is the circuit in which the post-sim results being obtained from

---------- Post added at 09:34 ---------- Previous post was at 07:52 ----------

this is the circuit in which the post-sim results being obtained from