allennlowaton

Full Member level 5

Hello EDA fellows,

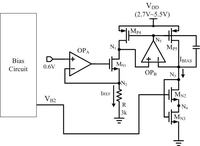

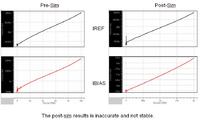

I've been doing the presim and the postsim of my Iref and Ibias circuit lately.(figure shown below)

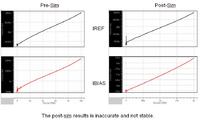

The problem now is the performance of the post-sim is unacceptable.

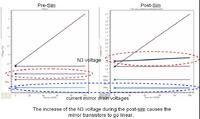

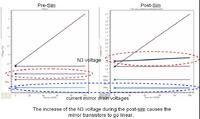

From the figure below, it can be seen that the voltage at N3 during the post-sim is almost twice as that

of the presim. I don't know if there's something wrong in my layout, though LVS had been passed.

Currently, the matching ratio of MP4 and MP5 is 1:20, I planned to reduce it to 1:2 which means I will increase the IREF value in order to obtain the same IBIAS value. Can you suggest an optimized matching ratio for this?

I've been doing the presim and the postsim of my Iref and Ibias circuit lately.(figure shown below)

The problem now is the performance of the post-sim is unacceptable.

From the figure below, it can be seen that the voltage at N3 during the post-sim is almost twice as that

of the presim. I don't know if there's something wrong in my layout, though LVS had been passed.

Currently, the matching ratio of MP4 and MP5 is 1:20, I planned to reduce it to 1:2 which means I will increase the IREF value in order to obtain the same IBIAS value. Can you suggest an optimized matching ratio for this?